# Research and Development of Event Building Farm for SuperKEKB

${ \begin{tabular}{l} Ko\ Ito\\ Department\ of\ Physics,\ University\ of\ Tokyo\\ \end{tabular} }$

February 4, 2005

#### Abstract

As an upgrade *B*-Factory experiment following the current ongoing Belle experiment, we are planning the SuperKEKB experiment with a luminosity of  $5 \times 10^{35} \text{cm}^{-2} \text{s}^{-1}$ , which is factor ten or more higher than the current Belle experiment. The current Belle DAQ system can not work efficiently at such a high event rate experiment.

We design a new DAQ system using an event building farm approach for the SuperKEKB experiment. We set up a prototype event building farm to study its performance. The event building farm consists of three parts, readout, distribution and full event building parts. If the number of the readout PC is eight, the prototype readout part works with the 30 kHz event rate which is the expected trigger rate at the start of the experiment. If the number of the readout PC is 20, the prototype readout part works with the 10 kHz event rate which is expected to be the maximum trigger rate. The distribution part tolerates the trigger rate of 30 kHz by increasing the number of the event builder units with the typical data size of 200 kB per event.

Based on this study, we consider the design specification and confirm that the designed event building farm satisfies the requirement at the SuperKEKB experiment. We conclude that the new DAQ system discussed in this thesis is the strong solution towards the high luminosity experiment at SuperKEKB.

# Contents

| 1 | Intr | oducti           | ion                                                        | 7  |

|---|------|------------------|------------------------------------------------------------|----|

| 2 | Sup  | $\mathbf{erKEI}$ | KΒ                                                         | 9  |

|   | 2.1  |                  | $\operatorname{olation}$                                   | 9  |

|   | 2.2  |                  | experiment                                                 | 10 |

|   |      | 2.2.1            | KEKB Accelerator                                           | 10 |

|   |      | 2.2.2            | Belle Detector                                             | 10 |

|   | 2.3  |                  | iew of SuperKEKB                                           | 15 |

|   | 2.0  | 2.3.1            | Physics motivation                                         | 15 |

|   |      | 2.3.2            | Accelerator                                                | 16 |

|   |      | 2.3.3            | Detector                                                   | 19 |

|   |      |                  |                                                            |    |

| 3 | Dat  | a Acq            | uisition System for SuperKEKB                              | 21 |

|   | 3.1  | Curre            | nt DAQ system of Belle                                     | 21 |

|   |      | 3.1.1            | Front-end Readout – Q-to-T and multi hit TDC               | 21 |

|   |      | 3.1.2            | Event Building – Switchless event building farm            | 23 |

|   |      | 3.1.3            | Mass Storage – High speed tape library                     | 25 |

|   | 3.2  | Overv            | iew of DAQ System for SuperKEKB                            | 25 |

|   |      | 3.2.1            | Requirements to DAQ for SuperKEKB                          | 25 |

|   |      | 3.2.2            | Problems of the Current DAQ System                         | 26 |

|   |      | 3.2.3            | Strategy of DAQ for SuperKEKB                              | 26 |

|   |      | 3.2.4            | Common Readout System                                      | 27 |

|   | 3.3  | Desgir           | of Event Building Farm for SuperKEKB                       | 28 |

|   |      | 3.3.1            | Multi-stage Event Building Farm                            | 28 |

|   |      | 3.3.2            | Software Architecture                                      | 32 |

| 4 | Dor  | formor           | nce Study of Stage1 Event Building                         | 35 |

| 4 | 4.1  |                  | Network Performance Study                                  | 35 |

|   | 4.1  | 4.1.1            | Setup for Basic Network Performance Study                  | 36 |

|   |      | 4.1.1            | Comparison of Network Switch Mode with Point-to-point Mode | 36 |

|   |      | 4.1.2            |                                                            | 38 |

|   | 4.2  |                  | Number of Connections vs. Throughput                       |    |

|   | 4.2  |                  | mance of Stage1                                            | 40 |

|   |      | 4.2.1            | Test Setup                                                 | 40 |

|   | 4.0  | 4.2.2            | Results of Performance Measurement of Stage1               | 41 |

|   | 4.3  | Summ             | ary of Stage1                                              | 45 |

CONTENTS

| 5 | 5 Performance Study of Stage2 Event Building      |       | 46     |

|---|---------------------------------------------------|-------|--------|

|   | 5.1 Requirements to Stage2                        |       | <br>46 |

|   | 5.2 Test Setup                                    | <br>• | <br>47 |

|   | 5.3 Results of Performance Measurement of Stage 2 |       | <br>49 |

|   | 5.4 Scalability                                   |       |        |

|   | 5.5 Comparison with Another Configuration         |       |        |

|   | 5.6 Modification of Distribution Network Matrix   |       |        |

|   | 5.7 Summary of Stage2                             |       | <br>59 |

| 6 | 6 Conclusions                                     |       | 60     |

|   | 6.1 Design Specification                          |       | <br>60 |

|   | 6.2 Conclusions                                   |       |        |

| A | A Cabibbo-Kobayashi-Maskawa Matrix                |       | 64     |

| В | B FINESSE and TTD                                 |       | 66     |

|   | B.1 FINESSE                                       | <br>• | <br>66 |

|   | B.2 TTD                                           |       | <br>66 |

# List of Figures

| 2.1  | The KEKB accelerator system.                                                                              | 10 |

|------|-----------------------------------------------------------------------------------------------------------|----|

| 2.2  | Schematic view of the Belle detector                                                                      | 11 |

| 2.3  | Side view of SVD2                                                                                         | 12 |

| 2.4  | Construction of the ACC and TOF                                                                           | 13 |

| 2.5  | Belle Level-1 trigger system                                                                              | 14 |

| 2.6  | The Feynman diagrams of $b \to s\ell^+\ell^-$ process                                                     | 15 |

| 2.7  | Forward-backward asymmetry in $B \to K^* \ell^+ \ell^-$ at 5 ab <sup>-1</sup> (a) and 50 ab <sup>-1</sup> |    |

|      | (b)                                                                                                       | 16 |

| 2.8  | Raw asymmetries for $B \to \phi K_S^0$ (close circle) and $B \to J/\psi K_S$ (open circle)                |    |

|      | at 5 ab <sup>-1</sup> . Input values are $S_{\phi K_S^0} = +0.24$ and $A_{\phi K_S^0} = +0.07$            | 17 |

| 2.9  | Conceptual view of an accelerator for SuperKEKB                                                           | 18 |

| 2.10 | KEKB accelerator upgrade plan. The horizontal axis and the vertical one                                   |    |

|      | are integrated luminosity and year, respectively                                                          | 19 |

| 2.11 | Side view of a detector for SuperKEKB                                                                     | 20 |

| 3.1  | Overview of Data flow scheme in the Belle experiment. The current Belle                                   |    |

| J.1  | DAQ comprises the front-end part (FASTBUS TDC, VME of each sub-                                           |    |

|      | detector), the event building part (E1xxx, E2xxx, E3), and the mass storage                               |    |

|      | part $(tape\ library)$                                                                                    | 22 |

| 3.2  | Principle of the Q-to-T technique                                                                         | 22 |

| 3.3  | A schematic view of the unified TDC readout system. The data from the                                     |    |

|      | Q-to-T system is read out by multi hit TDC and sent to the event builder.                                 | 23 |

| 3.4  | The distributions of the readout time for SVD, CDC, ECL, and KLM                                          | 24 |

| 3.5  | The dead time fraction as a function of the level-1 trigger rate. The typical                             |    |

|      | trigger rate is about 400 Hz at current Belle condition                                                   | 24 |

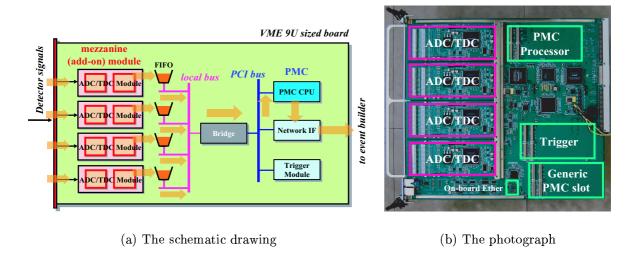

| 3.6  | The schematic drawing of DAQ system for SuperKEKB                                                         | 27 |

| 3.7  | The schematic drawing and the photograph of COPPER                                                        | 28 |

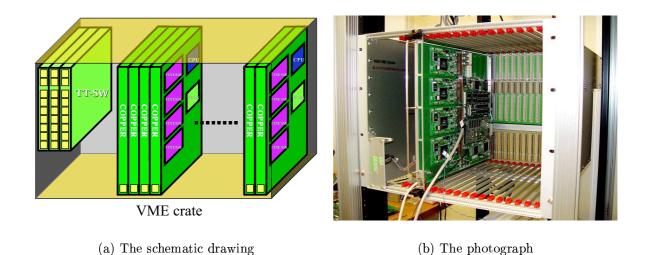

| 3.8  | The VME crate with the COPPER board                                                                       | 29 |

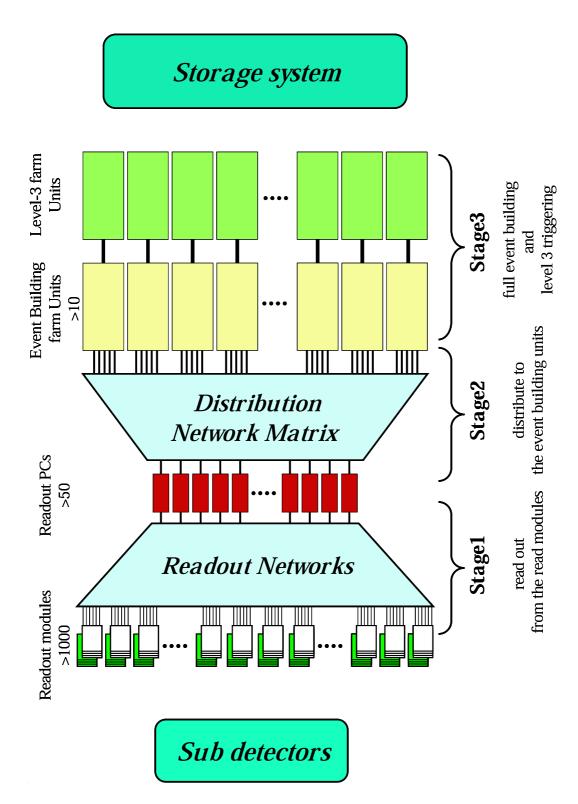

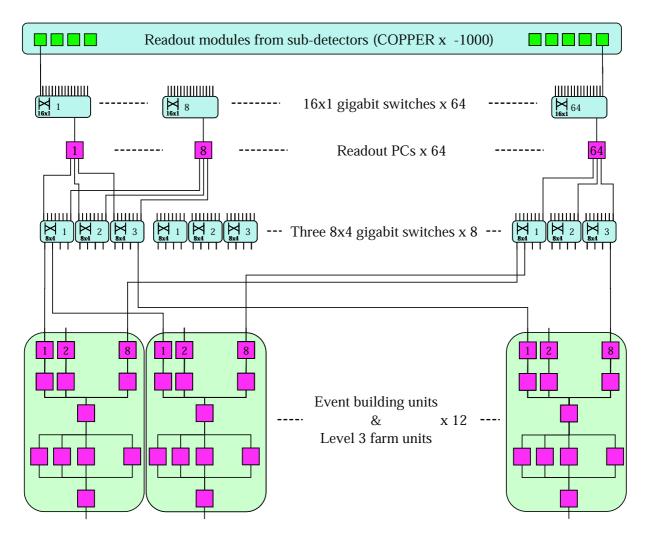

| 3.9  | Global design of the event building farm for SuperKEKB                                                    | 30 |

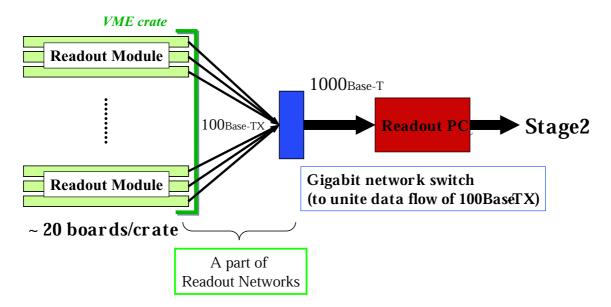

| 3.10 | The schematic drawing of a part of Stage1. The black arrow is a data                                      |    |

|      | flow. Stage1 consists of the readout modules (COPPER boards), a gigabit                                   |    |

|      | network switch and a readout PC                                                                           | 31 |

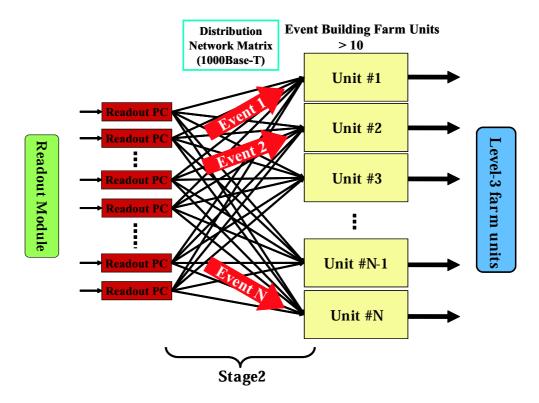

| 3.11 | 9 0                                                                                                       |    |

|      | network matrix and the layer-1 servers in the event building units                                        | 32 |

| 3.12 | The schematic drawing of one event building unit and one level-3 farm units                               | 33 |

| 3.13        | The software architecture for event building in the readout PC in case that<br>n-th sender PC are connected                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33       |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.14        | The schematic drawing of how the ring buffer works when the number of ring buffers is two.                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34       |

| 4.1         | The schematic drawings of the test configuration to study basic network performance                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36       |

| 4.2<br>4.3  | The picture of the network switch (upper) and the readout PC (lower) Comparison of the transfer rate of the network switch mode (blue) and that of the point-to-point mode (green) when the number of sender PCs is eight. The vertical axis shows the transfer rate and the horizontal axis shows the                                                                                                                                                                                                                                         | 37       |

|             | event size per sender PC. The horizontal solid line (red) is the maximum transfer rate of 100Base-TX (12.5 MB/s)                                                                                                                                                                                                                                                                                                                                                                                                                               | 37       |

| 4.4         | The transfer rate as a function of the number of connections. The dashed (red) lines and the dotted (blue) lines show the total transfer rate and the transfer rate per sender PC, respectively. The green lines show the                                                                                                                                                                                                                                                                                                                      |          |

|             | maximum transfer rate of 1000Base-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 38       |

| 4.5         | (a) The schematic drawing of data flow in network switch using two ports for output. (b) The transfer rate as a function of the number of connections. The dashed (red) line and the dotted (blue) line shows the total transfer                                                                                                                                                                                                                                                                                                               |          |

|             | rate and the transfer rate per Sender PC, respectively. The green line shows the maximum transfer rate of 1000Base-T (125 MB/s)                                                                                                                                                                                                                                                                                                                                                                                                                | 39       |

| 4.6<br>4.7  | The test bench setup for Stage1. The red arrows show the data flow The result of the performance study of Stage1 for variable number of sender PCs. The horizontal axis shows the event size. The vertical axis shows the event rate (a) and the transfer rate (b), respectively. (a): The red horizontal line is the typical trigger rate. The green horizontal line is the maximum trigger rate of 30 kHz. (b): The horizontal green line is the limit of 100Base-TX. The light green area shows typical event size area where the occupancy | 40       |

| 4.8         | of the drift chamber is assumed 10 % - 20 %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42       |

|             | trigger rates, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42       |

| 4.9         | The transfer rate per one sender (a) and the total transfer rate (b) as a function of the number of connections. The light blue dotted line (a) is a                                                                                                                                                                                                                                                                                                                                                                                           | 4.9      |

| <i>1</i> 10 | limit of 100Base-TX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43<br>44 |

|             | The schematic drawing of the receiver process of the readout PC using select function. One receiver process receives data from multiple TCP sockets.                                                                                                                                                                                                                                                                                                                                                                                           | 44       |

|             | The number of the sockets are one (left), two (middle) and four (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45       |

| 5.1         | The test configuration and data flow for Stage2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47       |

| 5.2         | The picture of the PCs which we use for the Stage2 study in KEK Tsukuba Hall B3                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48       |

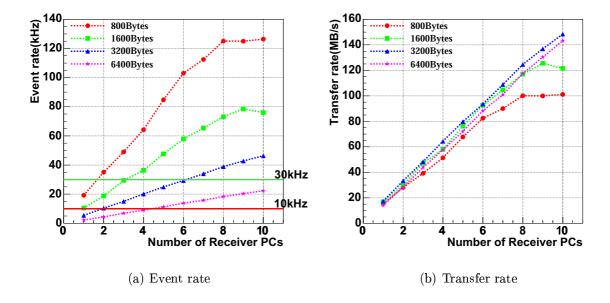

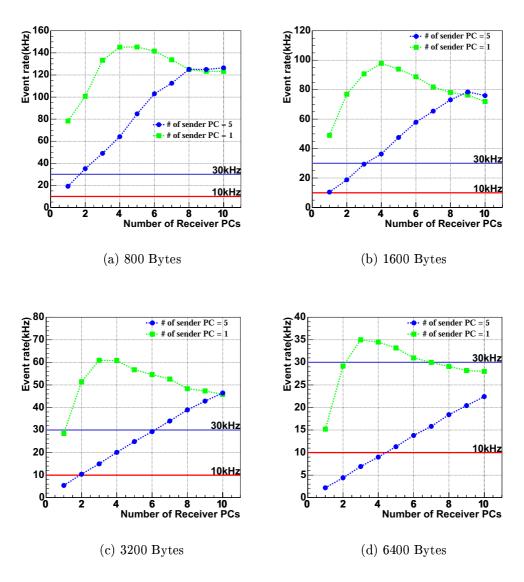

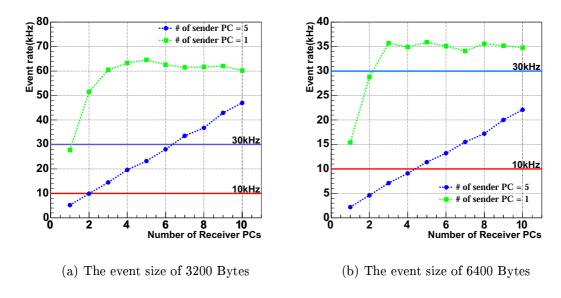

| 5.3  | The event rate (a) and the transfer rate (b) of the sender PCs as a function  |    |

|------|-------------------------------------------------------------------------------|----|

|      | of the event size varying the receiver PCs from one to ten when the number    |    |

|      | of the sender PCs is five. (a): The green and red horizontal lines show 30    |    |

|      | kHz and 10 kHz trigger rate, respectively                                     | 49 |

| 5.4  | The event rate (a) and the transfer rate (b) of the sender PC as a function   |    |

|      | of the number of the receiver PC when the number of the sender PCs is         |    |

|      | five. (a): The green and red horizontal lines show the 30 kHz and 10 kHz      |    |

|      | trigger rate, respectively                                                    | 50 |

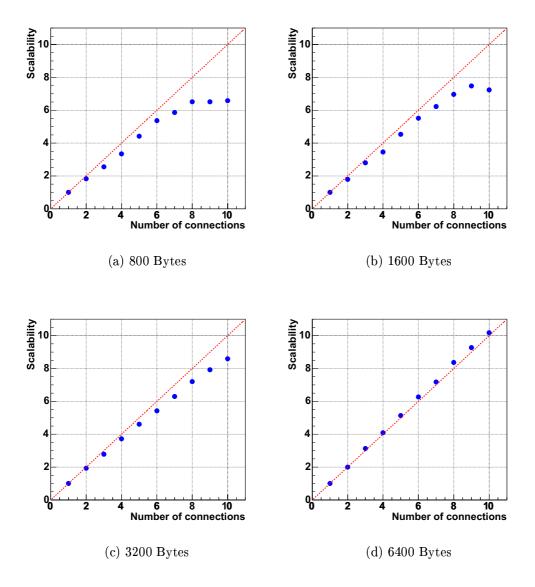

| 5.5  | The scalability as a function of the number of receiver PC when the number    |    |

|      | of the sender PC is five. The red dotted line is a line whose inclination of  |    |

|      | the straight line is one                                                      | 51 |

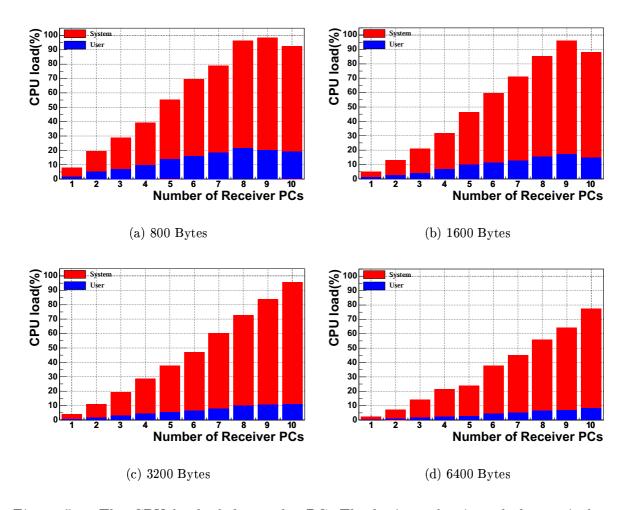

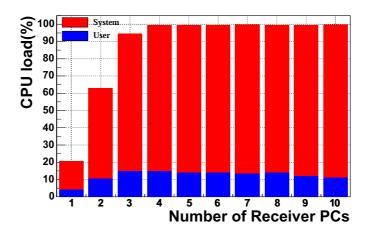

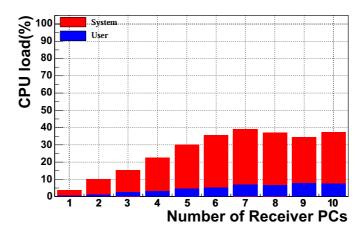

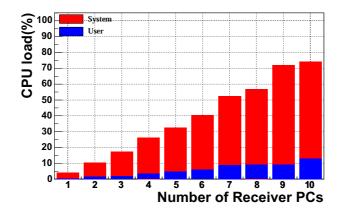

| 5.6  | The CPU load of the sender PC. The horizontal axis and the vertical one       |    |

|      | shows the number of the receiver PCs and the CPU load, respectively           | 52 |

| 5.7  | The setup of Stage2 and data flow when the number of the sender PCs is        |    |

|      | one                                                                           | 53 |

| 5.8  | The event rate as a function of the number of receiver PCs. The green line    |    |

|      | and the blues line show when the number of sender PC is one and five,         |    |

|      | respectively. The blue and red horizontal lines show 30 kHz and 10 kHz        |    |

|      | trigger rate, respectively                                                    | 54 |

| 5.9  | The CPU load of the sender PC with the event size of 3200 Bytes. The          |    |

|      | number of the sender PC is one                                                | 55 |

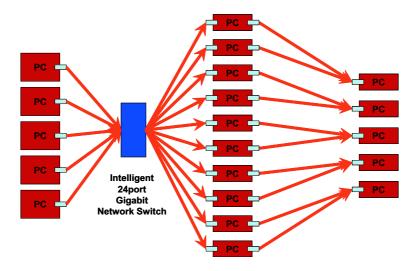

| 5.10 | The setup of Stage2 and data flow using one network switch                    | 55 |

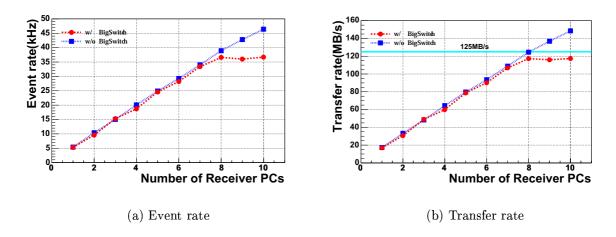

|      | The event rate and the transfer rate of sender as function of event size      | 56 |

|      | CPU load of the sender PC using one network switch                            | 56 |

|      | The setup of Stage2 and data flow modified the distribution network matrix    | 57 |

|      | The event rate of the sender PC as a function of the number of the receiver   |    |

|      | PCs with the improved distribution network matrix to be compared with         |    |

|      | Fig.??. The red and blue horizontal lines are 30 kHz and 10 kHz trigger rate. | 58 |

| 5.15 | CPU load of sender PC using the modified network matrix                       | 58 |

|      | ŭ                                                                             |    |

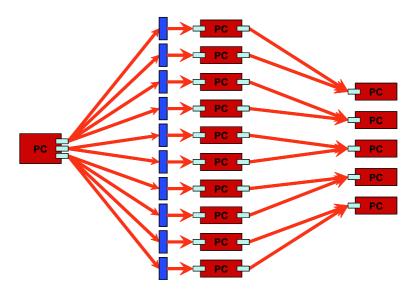

| 6.1  | The design specification of the event building farm for SuperKEKB. The        |    |

|      | Stage1 (readout part) consists of about 1000 COPPER, 64 gigabit network       |    |

|      | switch (only number 1, 8 and 64 are shown) and 64 readout PC (only            |    |

|      | number 1, 8 and 64 are shown). The Stage2 (distribution part) consists of     |    |

|      | 8 gigabit network switch in sets of three, and 12 units                       | 61 |

| A.1  | The unitary triangle of CKM matrix in the $B$ meson system $\dots \dots$      | 65 |

| B.1  | The schematic drawing of FINESSE                                              | 66 |

| B.2  | Overview of the TTD system                                                    | 67 |

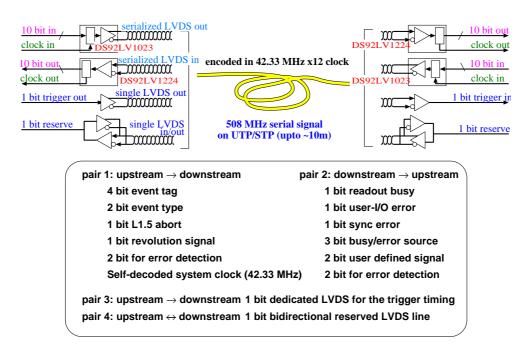

| B.3  | Format of the STP cable with two sets of serial-bus and two LVDS lines        | 68 |

# List of Tables

| 2.1 | Machine parameters of SuperKEKB                             | 17 |

|-----|-------------------------------------------------------------|----|

| 3.1 | The list of DAQ design parameters of Belle and SuperKEKB    | 25 |

| 4.1 | The comparison of the number of processes in the readout PC | 44 |

| 5.1 | Parameters of the PCs used for the performance study.       | 48 |

# Chapter 1

# Introduction

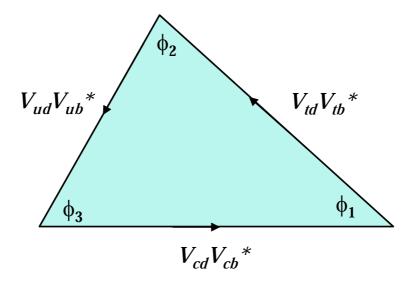

One of the most important discoveries in the modern elementary particle physics is the existence of the CP violation. The CP violation is expected to be related to the basic principle of the nature. It is expected to answer one of the most attractive questions in cosmology and in elementary particle physics, why the universe we currently live in consists predominantly of the matter. To observe the CP violation and to test the Kobayashi-Maskawa model in the B meson system, we started a B factory experiment, Belle, using the  $e^+e^-$  collider (KEKB) at the High Energy Accelerator Research Organization (KEK) in 1999.

In the summer of 2001, the presence of CP violation in the B meson system was established by the Belle and BaBar collaborations through the measurement of the time dependent CP asymmetry in the decay process of  $B^0(\overline{B}^0) \to J/\psi K_S^0$  [1, 2]. The Belle experiment also proved its ability to measure a number of decay modes of the B meson and other interesting observables; the precision measurement of interior angles of the unitary triangle, the semi-leptonic FCNC processes, and the existence of a new CP phase in the penguin process and so on. To collect many such observables, the KEKB has delivered the world highest luminosity of  $1.39 \times 10^{34} \text{cm}^{-2} \text{s}^{-1}$ , and the Belle has collected an integrated luminosity exceeding 300 fb<sup>-1</sup> data.

The KEKB luminosity is expected to be doubled in near future for many interesting physics decay modes that require larger data sample. To collect more large data sample, we are planning the SuperKEKB experiment with a luminosity of  $5 \times 10^{35} \mathrm{cm}^{-2} \mathrm{s}^{-1}$ , which is ten or more larger than that of the current KEKB.

In such a high luminosity, the level-1 trigger rate is expected to be 20 - 50 times higher than that of current trigger rate. The data size also is to be increased by a factor of six since a total channels of the Belle detector increase and so on. The number of readout modules (COPPER board), which is a pipelined readout electronics, is estimated more than 1000 if we assume that one COPPER board has a capacity of about 100 channels.

The current event building farm is not expected to work in these conditions because of a lack of the CPU power of the current system and no parallelization of data stream. Thus, it is necessary to develop a *scalable* and *tolerable* event building farm for the SuperKEKB experiment. To handle the high trigger rate, the large data size, and the large number of the COPPER boards, we design the event building farm for the SuperKEKB experiment. The designed event building farm employs the multi-stages for event building, which comprise Stage1 (readout stage), Stage2 (distribution stage), and Stage3 (full event

building stage), where Stage3 consists of multiple event building units that is based on the current event building farm and the reconstruction farm. Major change from the current event building farm is Stage1 and Stage2. To collect the event fragments the large number of the COPPER boards in the high rate, Stage1 constructs the readout network for data transmission with gigabit network switches. To distribute the event fragments to the unit event by event, Stage2 constructs the network matrix for the distribution of event with gigabit network switches. To decide the design specification, it is important to validate the design and measure the performance of Stage1 and Stage2.

In this thesis, we present the performance of Stage1 and Stage2 of designed event building farm including acceptable trigger rate, transfer rate, scalability of Stage2. We describe the brief introduction of the Belle experiment and the overview of SuperKEKB in Chapter 2, the data acquisition (DAQ) system for the SuperKEKB experiment including the current DAQ system in Chapter 3, the performance study of Stage1 in Chapter 4 and the performance study of Stage2 in Chapter 5, conclusion in Chapter 6.

# Chapter 2

# **SuperKEKB**

## 2.1 *CP* violation

Various symmetries play very important roles in particle physics. Some of them are continuous and the others are discrete. The CP symmetry is one of the latter and the origin of its violations is one of the most exciting mysteries in the present particle physics. As its name indicates, the CP transformation is a product of two discrete operations, C and P.

Charge conjugation, C, is a symmetry between particles and antiparticles. Parity, P, is a symmetry of space. P invariance means that the mirror image of an experiment yields the same result as the original.

Until 1956, it was believed that all elementary processes are invariant under C and P transformation. Lee and Yang pointed out the possibility of the violation of these symmetries, and subsequent experiments proved that C and P symmetries are really not conserved in weak interactions. However, the product of C and P transformations, CP was still considered to be a good symmetry. The second impact came in 1964. An experiment using neutral K mesons showed that CP is also not conserved under weak interactions [3]. Neutral K mesons ( $K^0$  and  $\overline{K}^0$ ) are created by strong interactions. The mass eigenstates of the  $K^0 - \overline{K}^0$  system can be written

$$|K_S\rangle = p|K^0\rangle + q|\overline{K}^0\rangle, |K_L\rangle = p|K^0\rangle - q|\overline{K}^0\rangle$$

(2.1)

(choosing the phase so that  $CP \mid K^0 \rangle = \mid \overline{K}^0 \rangle$ ). If the CP invariance is held, we would have p = q so that  $K_S$  would be CP even and  $K_L$  would be CP odd. Because the kaon is the lightest strange meson, it decays through the weak interaction. Neutral kaons can decay into two or three pions. Since pion has CP eigenvalue of -1,  $K_L$  always decays into two pions, if CP is conserved in weak interactions. The experiment performed at Brookhaven proved that a small faction of  $K_L$  decays into two pions, which means CP is violated in the weak interaction. In the kaon system, the order of observed CP asymmetry is about  $10^{-3}$ .

# 2.2 Belle experiment

The primary goal of the B factory experiment [7] is to establish the CP violation in the B meson system. The KEKB accelerator [8] is an energy-asymmetric  $e^+e^-$  collider to produce B mesons. The decay products of B mesons are detected by the Belle detector.

#### 2.2.1 KEKB Accelerator

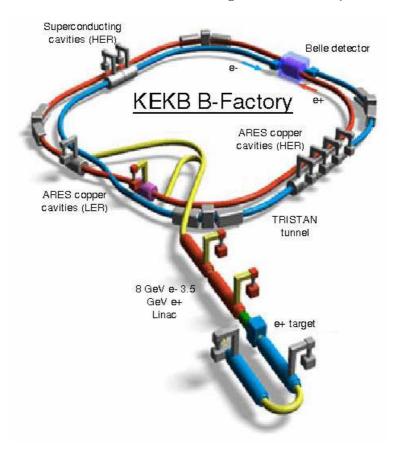

The KEKB accelerator has two rings in a tunnel which used for TRISTAN. The total length of the accelerator main rings is 3 km. Beam energies are chosen to be 8.0 GeV for the electron and 3.5 GeV for the positron, so that the center of mass energy comes on the  $\Upsilon(4S)$  resonance and  $\beta\gamma\simeq 0.425$  corresponds to the flight length of the B meson decays of approximately 200  $\mu$ m. Configuration of KEKB accelerator is shown in Fig 2.1. In May, 2003, KEKB has achieved the design luminosity,  $10^{34} {\rm cm}^{-2} {\rm s}^{-1}$ . As of the end of 2004, the peak luminosity is  $1.39\times 10^{34} {\rm cm}^{-2} {\rm s}^{-1}$ . The integrated luminosity exceed 300 fb<sup>-1</sup> data.

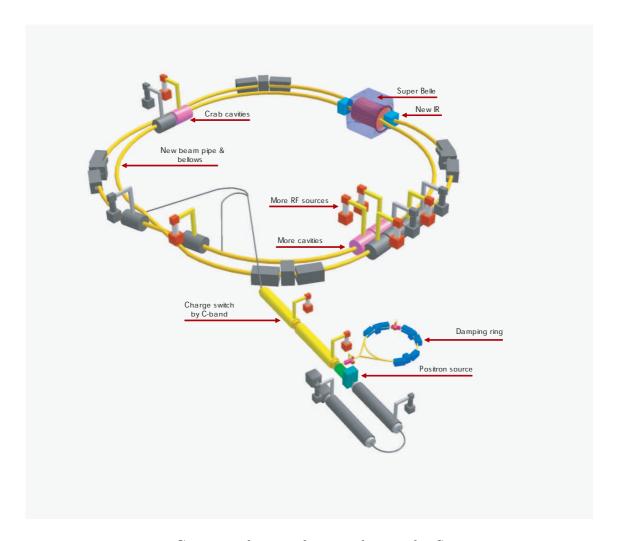

Figure 2.1: The KEKB accelerator system.

#### 2.2.2 Belle Detector

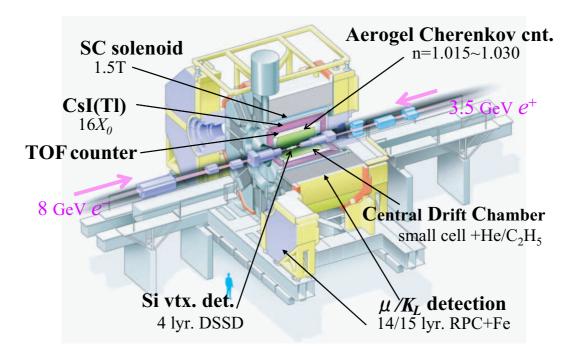

The Belle detector is a detector designed for the study of the CP violation in the B meson system. The Belle detector consists of a silicon vertex detector (SVD), a 50-layer

central drift chamber (CDC), an array of aerogel threshold cherenkov counters (ACC), time-of-flight scintillation counters (TOF), an electromagnetic calorimeter composed of CsI(Tl) crystals (ECL), a  $K_L^0$  and muon detectors (KLM), and a pair of extreme-forward calorimeters (EFC). Figure 2.2 is the schematic view of the Belle detector.

Figure 2.2: Schematic view of the Belle detector.

#### Sub detectors

#### SVD

SVD is a vertex detector with precise vertex resolution. The measurement of CP asymmetry parameters requires that the resolution of vertex detector is better than the average flight distance of B meson, which is about 200  $\mu$ m at the KEKB accelerator.

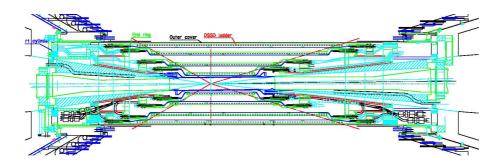

In summer of 2003, SVD system was upgraded to SVD2 [9]. SVD2 consists of four layers of silicon ladders with covering polar angle from 17° to 150°. The momentum dependence of the impact parameter resolution of SVD2 is described by  $\sigma_{r\phi} = 21.9 \oplus 35.5/(p\beta sin^{\frac{3}{2}}\theta)[\mu m]$  and  $\sigma_z = 27.8 \oplus 31.9/(p\beta sin^{\frac{5}{2}}\theta)[\mu m]$  with cosmic ray muons. The number of channel is about 110,000 in total. Figure 2.3 show r-z view of SVD2.

#### CDC

The main role of CDC is the detection of charged particle tracks and the reconstruction of its momentum. CDC also take part of particle identification information by measuring dE/dx. The polar angle coverage of CDC cover from 17° to 150°. In summer 2003, the inner most three layers were replaced with a new chamber in order to provide a space for

Figure 2.3: Side view of SVD2.

SVD2. The new chamber consists of small cells of 5 mm  $\times$  5 mm in dimension to reduce the occupancy. The number of channel is about 9,000 in total.

#### ACC

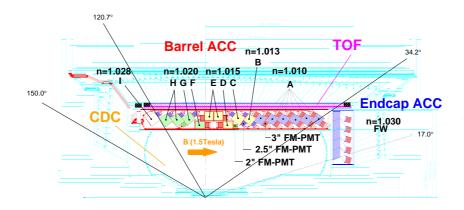

ACC is to separate kaons from pions for momentum region in  $1.2 . The aerogel of the ACC is made of SiO<sub>2</sub> whose refractive index is <math>n \simeq 1.015$ .

In general, the threshold of Cherenkov light emission in the matter with the refractive index of n is represented using the velocity of particle  $\beta$  as follows:

$$n > 1/\beta = \sqrt{1 + (m/p)^2},$$

(2.2)

where the particle momentum p is measured by CDC, m is the particle mass. The particle can be identified whether it emitted a light or not. ACC is divided into two parts. A barrel array covers an angular range of  $34^{\circ} < \theta < 127^{\circ}$ , and a forward end-cap array covers an angular range of  $17^{\circ} < \theta < 34^{\circ}$ . The number of channel is about 2,200 in total. The side view of ACC is shown in Fig. 2.4.

#### TOF

TOF, which is made of a plastic scintillation counter, is also used for the particle identification. It has responsibility to identify the charged particles, whose momentum is less than  $1.2~{\rm GeV}/c$ . The relation between the measured flight time T and the particle mass is as follows:

$$T = \frac{L}{c}\sqrt{1 + (m/p)^2},$$

(2.3)

where L is flight length. In the Belle, L is 1.2 m. The polar angle coverage of TOF is from 34° to 121°. Also TOF system has one another sets of scintillation counters, which are used to generate the trigger signal. The number of channel is about 400 in total. The side view of TOF is shown in Fig. 2.4.

#### ECL

The main purpose of the ECL is to detect photons and the identification of electrons from B meson decays with high efficiency and good energy resolution. ECL is made of CsI(Tl) crystals.

Figure 2.4: Construction of the ACC and TOF.

ECL is also used for the measurement of the luminosity by Bhabha scattering, which yields high energy electrons. Thus ECL covers the energy range widely from 20 MeV to 8 GeV. The number of channel is about 9,000 in total.

#### KLM

KLM is the outermost detector to detect  $K_L^0$  and muon, and to measure their position. KLM consists of an alternating sandwich of 4.7 cm thick iron plates and resistive plate counters (RPCs) located outside the superconducting solenoid. KLM covers an angle range  $25^{\circ} < \theta < 145^{\circ}$ . The number of channel is about 45,000 in total.

#### **EFC**

EFC measures the energy of photons and electrons at the extreme forward (backward) direction outside the ECL acceptance. EFC covers  $6.4^{\circ} < \theta < 11.5^{\circ}$  in the forward direction and  $163.3^{\circ} < \theta < 171.2^{\circ}$  in the backward direction. We use BGO (Bi<sub>4</sub>Ge<sub>3</sub>O<sub>12</sub>) crystals for EFC, because EFC is expose in the high irradiation (about 5 MRad per year) of photons from the synchrotron radiation and the spent electrons. The number of channel is about 320 in total.

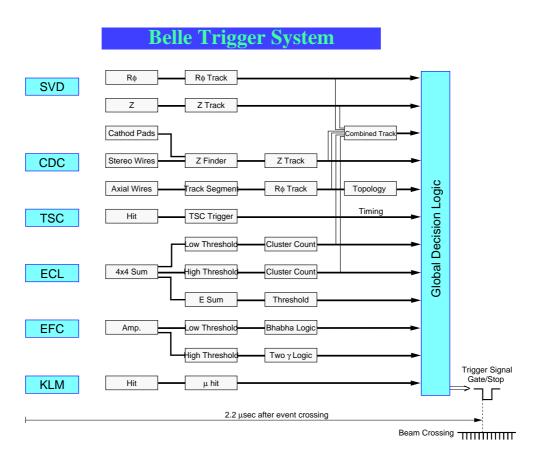

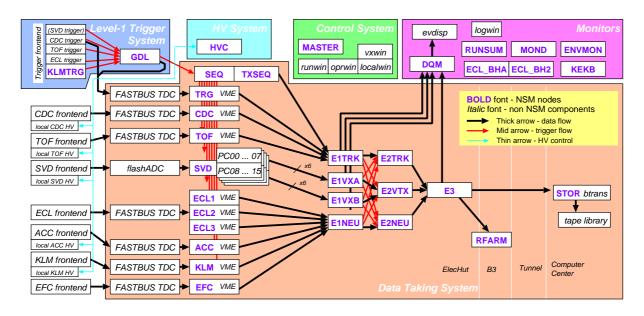

#### Trigger

The Belle trigger system mainly consists of the Level-1 hardware trigger and the Level-3 software trigger. Figure 2.5 shows the the block diagram of Level-1 trigger system. It consists of the 6 sub-detector trigger systems and the central trigger system called the Global Decision Logic (GDL). The trigger system provides the trigger signal with the fixed time of 2.2  $\mu$ s after the event occurrence. The average trigger rate of current Belle experiment is about 400Hz at the luminosity of  $10^{34}$ cm<sup>-2</sup>s<sup>-1</sup>.

Figure 2.5: Belle Level-1 trigger system.

# 2.3 Overview of SuperKEKB

In order to search for a new physics beyond the Standard Model through the rare B decays, the upgrades of the accelerator and the detector are proposed as SuperKEKB project. The SuperKEKB aim 30 times higher luminosity than the current KEKB accelerator. We expect an annual integrated luminosity of 5 ab<sup>-1</sup> assuming 100 days of operation. This section gives a brief description of a physics motivation, accelerator and detector of the SuperKEKB.

#### 2.3.1 Physics motivation

We show two brief introduction of many physics motivations of SuperKEKB. The details can be found elsewhere [10].

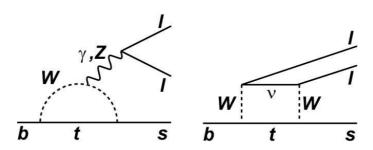

$$b \to s \ell^+ \ell^-$$

The  $b \to s \ell^+ \ell^-$  process is one of the Flavor Changing Neutral Current (FCNC) processes. In the Standard Model, FCNC processes are forbidden at tree level. However, higher order diagrams, such as penguin diagrams and box diagrams, induce FCNC within the Standard Model (see Fig. 2.6). Such loop diagrams are expected to be sensitive to a new physics. Since heavy particles beyond the Standard Model could contribute to the additional loop diagrams, various parameters, such as branching ratio, may well be deviated from the expected value by the Standard Model.

Figure 2.6: The Feynman diagrams of  $b \to s\ell^+\ell^-$  process

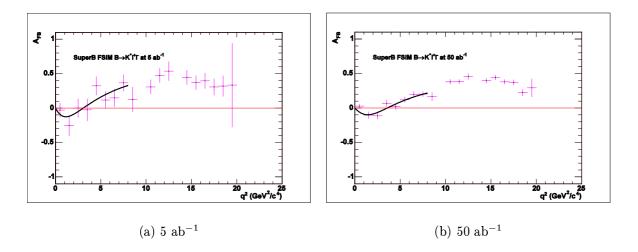

The one target of the SuperKEKB for this process is the forward-backward asymmetry. The forward-backward asymmetry in  $B \to K^* \ell^+ \ell^-$ , defined as

$$\overline{A}_{FB}(q^2) = \frac{N(q^2; \theta_{B\ell^+} > \theta_{B\ell^-}) - N(q^2; \theta_{B\ell^+} < \theta_{B\ell^-})}{N(q^2; \theta_{B\ell^+} > \theta_{B\ell^-}) + N(q^2; \theta_{B\ell^+} < \theta_{B\ell^-})},$$

(2.4)

is an ideal quantity to disentangle the Wilson coefficients  $C_9$  and  $C_{10}$  together with the sign of  $C_7$ , where q is the dilepton mass. Within the Standard Model, there is a zero crossing point of forward-backward asymmetry in the low dilepton invariant mass region, while the crossing point may disappear in some SUSY scenarios. Another important new physics effect can be searched for by using the  $B \to K^* \ell^+ \ell^-$  or  $B \to X_s \ell^+ \ell^-$  forward-backward asymmetry; SN(2) single down-type quarks and tree-level Z flavor-changing-neutral-current.

Figure 2.7 shows the expected  $\overline{A}_{FB}$  at 5 ab<sup>-1</sup> and 50 ab<sup>-1</sup> as a function of  $q^2$ . It can be seen that the crossing pattern of the forward-backward asymmetry will be already visible at 5 ab<sup>-1</sup> and will be clearly observed at 50 ab<sup>-1</sup>.

Figure 2.7: Forward-backward asymmetry in  $B \to K^* \ell^+ \ell^-$  at 5 ab<sup>-1</sup> (a) and 50 ab<sup>-1</sup> (b).

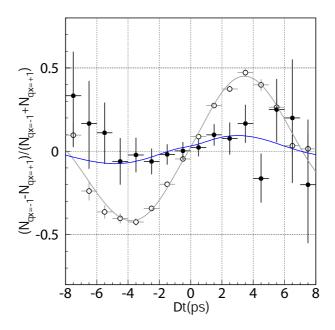

$b \to sq\overline{q}$

The recently observed disagreement between the value of the angle  $\phi_1$  measured in the penguin process  $B \to \phi K_S^0$  and the precisely measured value in  $B \to J/\psi K_S^0$  suggests the existence of a new CP phase in the penguin process  $b \to sq\overline{q}$ . The  $B \to \phi K_S^0$  decay, which is dominated by the  $b \to ss\overline{s}$  transition, is an especially unambiguous and sensitive probe of new CP-violating phase from physics beyond the Standard Model.

Figure 2.8 shows an example of a fit to events in a MC pseudo-experiment for the  $B\to \phi K^0_S$  and  $J/\psi K^0_s$  decays at 5 ab<sup>-1</sup>. The large deviation can be observed with a single decay channel  $B\to \phi K^0_S$  at the SuperKEKB.

#### 2.3.2 Accelerator

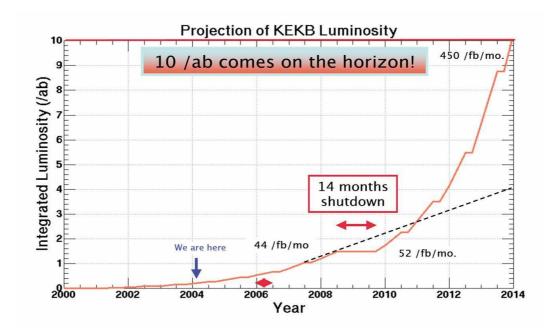

Figure 2.9 shows the conceptual view of an accelerator for the SuperKEKB [10]. The design luminosity of the SuperKEKB is  $1 - 5 \times 10^{35}$  cm<sup>-2</sup>s<sup>-1</sup>. The SuperKEKB collider will be constructed by re-using most of the components of KEKB accelerator, in particular the ring magnets and klystrons used to supply RF power to the cavities. But, there are many components that need to be modified or newly developed; RF system, vacuum system, feedback system and so on. A crossing angle of the current KEKB accelerator is 30 mrad in order to keep the beam separated. The crab crossing scheme, which effectively creates a head-on collision, will be used at SuperKEKB. Beam energy exchange, with electrons injected to the LER instead of the HER and positrons injected to the HER, is also under consideration to reduce the effect of the photo-electron cloud and to minimize the injection time. The machine parameters of SuperKEKB is shown in Table 2.1. Figure 2.10 shows the plan of the KEKB accelerator upgrade.

Figure 2.8: Raw asymmetries for  $B\to \phi K^0_S$  (close circle) and  $B\to J/\psi K_s$  (open circle) at 5 ab<sup>-1</sup>. Input values are  $S_{\phi K^0_S}=+0.24$  and  $A_{\phi K^0_S}=+0.07$ .

Table 2.1: Machine parameters of SuperKEKB

| Parameters               | LER / HER                                   | Unit                                        |

|--------------------------|---------------------------------------------|---------------------------------------------|

| Beam energy              | $3.5~({ m e^-})~/~8.0~({ m e^+})$           | ${ m GeV}$                                  |

| Beam current             | 9.4 / 4.1                                   | $\mathbf{A}$                                |

| Particles/bunch          | $1.18 \times 10^{11} / 5.13 \times 10^{10}$ |                                             |

| Number of bunch          | 5018                                        |                                             |

| Horizontal $\beta$ at IP | 0.2                                         | m                                           |

| Vertical $\beta$ at IP   | 0.003                                       | $\mathbf{m}$                                |

| Horizontal emittance     | 24                                          | nm                                          |

| Crossing angle           | $0 \; (crab)$                               | $\operatorname{mrad}$                       |

| Luminosity               | 5                                           | $\times 10^{35} {\rm cm}^{-2} {\rm s}^{-1}$ |

Figure 2.9: Conceptual view of an accelerator for SuperKEKB.

Figure 2.10: KEKB accelerator upgrade plan. The horizontal axis and the vertical one are integrated luminosity and year, respectively.

#### 2.3.3 Detector

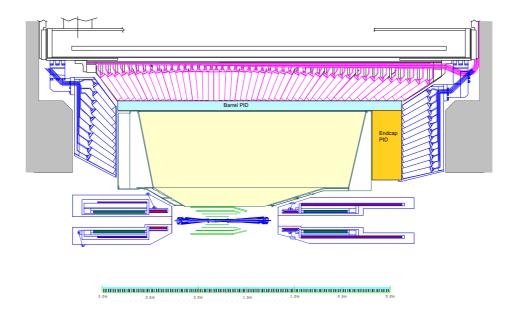

Figure 2.11 shows the conceptual view of a detector for SuperKEKB. The upgraded Belle detector for SuperKEKB consists of vertex detector, central tracker, particle identification detector, calorimeter, and  $K_L$  and muon detector. In order to maintain and to evolute the current performance in the higher background environment, each detector is upgraded gradually. We introduce the detail of DAQ system for SuperKEKB in Section 3.2. The detail of another detectors can be found elsewhere [10].

Figure 2.11: Side view of a detector for SuperKEKB.

# Chapter 3

# Data Acquisition System for SuperKEKB

In this chapter, we describe the data acquisition (DAQ) system of Belle and SuperKEKB. The current Belle DAQ system is given in Section 3.1. In Section 3.2, the problems of Belle DAQ system toward SuperKEKB and the overview of the DAQ system for SuperKEKB except the event building farm is described. The event building farm for SuperKEKB is written in Section 3.3.

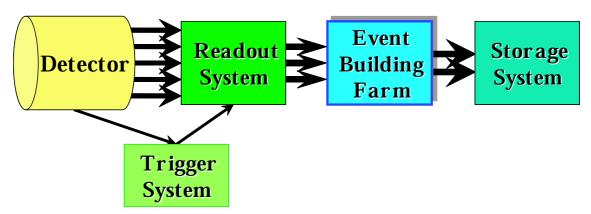

# 3.1 Current DAQ system of Belle

The Belle DAQ system deals with the data flow from the analog signals by the individual sub-detectors of Belle to their digitized data to save in mass storage for offline analysis. Figure 3.1 shows the global data flow scheme of the Belle experiment. We can divide the Belle DAQ system into three parts: a front-end readout part, an event building part and a mass storage part. In the front-end readout part, detector outputs are digitized and the digitized data are sent to event building part. Then the event building part works to construct one event data from the data of individual sub-detectors. In the mass storage part, the built data are recorded to a tape library.

# 3.1.1 Front-end Readout – Q-to-T and multi hit TDC

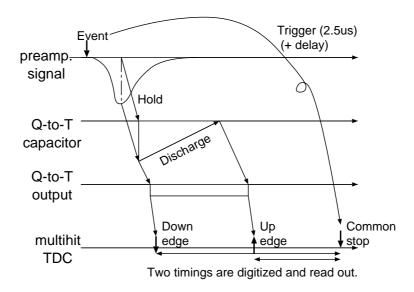

The front-end readout part in Belle DAQ system takes care of the analog signals from individual sub-detectors in the Belle experiment and digitizes them [11]. The analog signals from sub-detectors except SVD are digitized by a unified readout system based on the Q-to-T conversion with FASTBUS TDCs [12, 13]. The principle of a Q-to-T technique is shown in Fig.3.2. A signal from a detector is connected to a capacitor. When the signal reaches the peak, the capacitor holds and start discharging. The output pulse width indicates the pulse hight of the original signal, and the leading edge (down edge) indicates the timing of the original signal. So we can measure both the timing and the height with one channel of TDC. The Q-to-T technique is effective to reduce the number of readout channels. For timing digitization, we use multi hit TDC LeCroy 1877S, which has 96 channels and holds up to 16 hits per channel.

Figure 3.1: Overview of Data flow scheme in the Belle experiment. The current Belle DAQ comprises the front-end part (*FASTBUS TDC*, VME of each sub-detector), the event building part (E1xxx, E2xxx, E3), and the mass storage part (*tape library*)

Figure 3.2: Principle of the Q-to-T technique

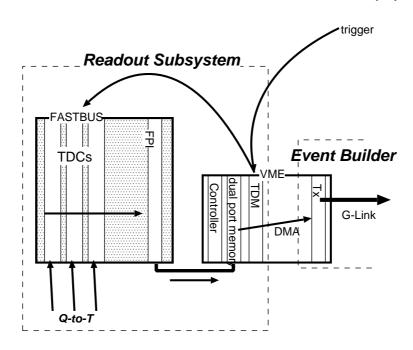

Digitized data are sent to a VME crate by a FASTBUS Processor Interface (FPI) and transfered to the event building farm through a 100base-TX network (see Fig. 3.3). One FASTBUS crate has one FPI, and the subsystem controller on VME requests all FPIs to collect data from TDC modules. The data from SVD are processed with a PC-based readout system and sent to the event building farm via the network [14].

Figure 3.3: A schematic view of the unified TDC readout system. The data from the Q-to-T system is read out by multi hit TDC and sent to the event builder.

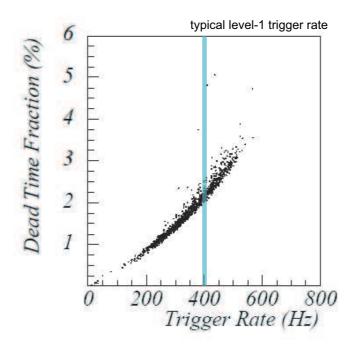

The current Belle readout system is not pipelined and, it has a readout dead time since we use the gate and delay method. The Figure 3.4 shows the distributions of readout time for some of detectors during when the data cannot be record. The readout time for SVD is almost fixed 30  $\mu$ sec. The time for other detectors consists of two components. One is the constant latency caused by the readout overhead which is around 30  $\mu$ sec. The other is the component which is proportional to data size and makes the tail component in the distribution. The relation between the total dead time fraction and the level-1 trigger rate is shown in Fig. 3.5. At a typical trigger rate of 400 Hz, the fraction of the dead time is around 2 %, which is reasonably small for the data acquision of the Belle experiment.

# 3.1.2 Event Building – Switchless event building farm

The event building part proceeds background reduction and form event data. We use a "switchless" system in which we connect all PCs in the point-to-point mode [15], to avoid any network congestion. The event building farm consists of three layers of PC servers (see Fig. 3.1). The first layer servers receive the data from the front-end readout part, perform a partial event building and carries out a software trigger (Level 2.5 trigger) processing using the partially built event data. The trigger signal is sent to the second layer servers to reject the event data. The second layer servers decide to send the event data to the third

Figure 3.4: The distributions of the readout time for SVD, CDC, ECL, and KLM

Figure 3.5: The dead time fraction as a function of the level-1 trigger rate. The typical trigger rate is about 400 Hz at current Belle condition.

layer server or discard them. The third layer server performs final event data construction and the online event selection [18]. The selected event is sent to the storage system. The current *switchless* event building farm is working well at the typical Belle trigger rate of 400 Hz(see Fig. 3.5). All PCs except third layer server of the current event building farm are equipped with four Intel Pentium CPU operating 700 MHz. The third layer server is equipped with two Intel Xeon CPU operating 3.06 GHz.

### 3.1.3 Mass Storage – High speed tape library

Sony Petasite tape library system with Sony DTF2 drivers is used as the mass storage system. We use SPARC workstations as the storage servers in order to use the tape library control software for Solaris operating system. We confirmed that the DTF2 drive provides the designed write speed of 24 MB/sec.

# 3.2 Overview of DAQ System for SuperKEKB

In this section, we describe the problems of the Belle DAQ system and the DAQ system for SuperKEKB. We show the requirement of the DAQ system for SuperKEKB in Subsection 3.2.1. We show the problems of the current Belle DAQ system in Subsection 3.2.2. The strategy of the DAQ system for SuperKEKB is written in Subsection 3.2.3. The readout system for SuperKEKB is described in Subsection 3.2.4. We show the overview and the design of event building farm for SuperKEKB in next Section.

## 3.2.1 Requirements to DAQ for SuperKEKB

The requirement of the DAQ system for the SuperKEKB experiment is much tighter than that of the Belle experiment. Table 3.1 shows the comparison of the design parameters of the DAQ systems between Belle and SuperKEKB.

|                               | Belle                | SuperKEKB                   |

|-------------------------------|----------------------|-----------------------------|

| Luminosity( $cm^{-2}s^{-1}$ ) | $1.4 \times 10^{34}$ | $5 \times 10^{35}$          |

| Physics trigger rate          | $140~\mathrm{Hz}$    | 1-5  kHz                    |

| Maximum trigger rate          | $500~\mathrm{Hz}$    | $10\text{-}30~\mathrm{kHz}$ |

| Event size at L1              | 40 kB/event          | 200-300  kB/event           |

| Data flow rate at L1          | 20  MB/sec           | > 2  GB/sec                 |

| Data flow rate at storage     | 10  MB/sec           | < 250  MB/sec               |

Table 3.1: The list of DAQ design parameters of Belle and SuperKEKB.

At the SuperKEKB experiment, the level-1 trigger rate is expected to be 10-30 kHz which is twenty times and more higher than the Belle experiment. The event size is expected to increase to 200-300 kB/event from current event size of 40 kB/event at the Belle, since 1) the number of channels will be increased and 2) we plan to sample the waveform of output signals for some sub-detectors. Due to the higher luminosity and the inflated event size, the data flow rates at the level-1 trigger is more than 2 GB/sec which is factor hundred and more higher than that of the Belle experiment. We need a novel

system to handle such a high data flow rate. A system clock of the readout timing is chosen to be 42.33 MHz, one twelfth of the SuperKEKB RF clock of 508 MHz. These parameters depend on the luminosity increase of SuperKEKB.

### 3.2.2 Problems of the Current DAQ System

Although the current Belle DAQ system works well for the current Belle condition, there are several problems that prevent us from scaling up the system to be used in the - 30 times higher luminosity of  $5 \times 10^{35} {\rm cm}^{-2} {\rm s}^{-1}$ . For example, a linear extrapolation of the dead time fraction of current Belle system gives the dead time of more than 50 % (see Fig. 3.5). We think there are three limitation to use the Belle DAQ system at the SuperKEKB experiment.

The first limit comes from the front-end electronics and their readout. In the current FASTBUS-TDC based system using Q-to-T technique, it takes about 30  $\mu$ sec in total to read out the TDC data of one event. This is too long when we need to handle 10 - 30 kHz trigger rate. Hence, we need a new deadtime-less readout system, which has pipeline buffer instead of gate and delay method.

The second limit is in the event building farm. The current event building farm is based on PCs connected one another via TCP/IP network without any large-scale network switch. The current event building farm is not scalable to the 30 times larger luminosity even if the PC performance is improved. Actually, we assume that the performance of the event building farm will saturate at a trigger rate of 600 - 700 Hz, which corresponds to a luminosity of about  $2 \times 10^{34} {\rm cm}^{-2} {\rm s}^{-1}$  because of a lack of CPU power of the current event building farm. A parallel data processing is required to solve the problem.

The third limit is in the data storage. We expect the data storage rate will be 250 MB/s in the SuperKEKB. The current maximum data storage rate is 24 MB/s using high speed tape device.

The design strategy to overcome these limitations is discussed in the following subsection.

# 3.2.3 Strategy of DAQ for SuperKEKB

We need to develop a new DAQ system to satisfy the requirements listed in the subsection 3.2.1 for the SuperKEKB experiment. We still plan to keep the design concept of the current Belle event building farm as much as possible. The DAQ system consists of readout, event building farm and the storage parts. Each parts have difficulties toward the SuperKEKB experiment as described in the previous section. The new DAQ system must have the following features:

- Pipelined readout,

- Separated data streams, and

- Parallel data record devices.

The design strategies for the requirements are as follows:

- 1. Employ the pipeline based readout electronics to keep data taking during trigger decision.

- 2. Use of common readout platform as possible to handle the pipelined readout electronics.

- 3. Build up events in multi stages to manage the large number of readout modules and the large data size.

- 4. Adopt unit-style event building module to construct a scalable system to work with the luminosity increase.

- 5. Record the data onto disk directly.

The first and second strategies are to reduce the dead time of the readout and to ease the maintenance for the readout part. The third and forth strategies are to have DAQ processing scalability and to disperse the data flow in the event building farm part. The fifth strategy is to overcome the requirement of the data storage rate at the storage part.

Figure 3.6 show the schematic drawing of DAQ system. In the following subsections, we discuss the readout system and the event building farm system.

Figure 3.6: The schematic drawing of DAQ system for SuperKEKB.

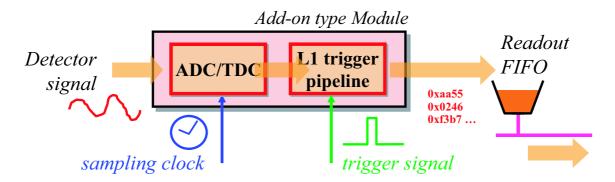

## 3.2.4 Common Readout System

To take care of the event rate of 30 kHz with the event size of 300 KB, a pipelined readout system is essential to handle the high trigger rate of 30 kHz with a low dead time. The readout system consists of a set of modularized common readout platform called a common pipeline platform for electronics readout (COPPER) [17]. The COPPER board is a VME 9U board to mount digitizer modules, a trigger timing receiver, a CPU module used for the on-board data processing.

Figure 3.7 shows a schematic drawing and a photograph of COPPER. One COPPER board is equipped with four slot for digitizer modules, four readout FIFOs for event buffering, and three PCI mezzanine card (PMC) slot. The CPU module on the COPPER board is a commercially available PMC module. It can be easily upgraded to use an up-to-date

CPU to increase the processing power. Many commercial PMC products are available; Ethernet cards, Gigabit Ethernet cards, memory modules and so on.

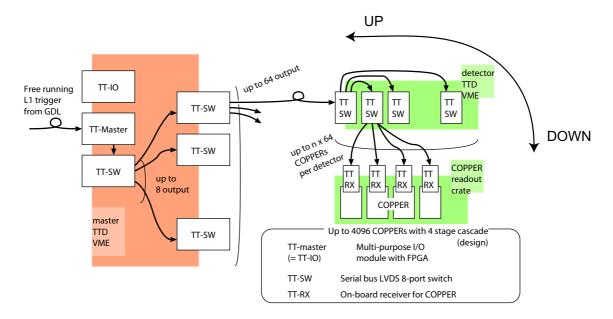

The digitizer modules are equipped with a L1 pipeline FIFO so as to record the digitized signal without readout dead time (see Appendix B). The L1 trigger signal is distributed to every COPPER module. The COPPER boards are received the L1 trigger signal by the trigger timing receiver from *Trigger Timing Distribution* system(see Appendix B).

Figure 3.7: The schematic drawing and the photograph of COPPER.

At SuperKEKB, the number of the COPPER boards is considered to be an order of 1,000. The total number of channels of central drift chamber for SuperKEKB is expected to be about 15,000 channels. Thus the number of the COPPER boards for central drift chamber is about 150 if the number of channels of one COPPER is assumed to be about 100. Figure 3.8 shows the picture of the COPPER with VME crate. One VME crate has 16 9U slot for the COPPER board and four 6U slot for trigger modules. The digitized data by digitizer modules are sent to the event building farm through the Ethernet of the COPPER board.

# 3.3 Desgin of Event Building Farm for SuperKEKB

In this section, we describe the event building farm for SuperKEKB and the software architecture for event building.

# 3.3.1 Multi-stage Event Building Farm

To perform the event building and data reduction with the > 1000 readout modules with the trigger rate of - 30 kHz, we design a multi-stage event building and multiple unit structure. Figure 3.9 shows the global design of the event building farm for SuperKEKB. The designed event building system consists of three stages; Stage1, Stage2, and Stage3. At Stage1 (readout stage), event fragments are gathered from the readout modules to

Figure 3.8: The VME crate with the COPPER board.

manage the large number of readout modules. At Stage2 (distribution stage), to have the scalability, the gathered event fragments are sent to one of the event building units, which are located in parallel at Stage3. At Stage3 (full building stage), the event fragments from Stage2 are built to form an event and the built event is sent to one of the level-3 farm units.

The purposes and the functionalities of each stages are summarized below.

#### Stage1 (Readout Stage)

Stage1 indicates the readout networks, which is to collect the event fragments from readout modules. For easy maintenance and cost and space reduction, the number of readout PCs have to be as small as possible. We employ small network switches in this stage. An overview of a part of Stage1 is shown in Fig. 3.10. Digitized signals from the front-end electronics of each sub-detector are first fed into the readout modules. The triggered data are then sent to the readout PCs via a network switch. The network switch is connected with 20 readout modules, this number corresponds to one VME create, by 100Base-TX. Each of readout modules and the network switch are connected by 100Base-TX, and the switch and the readout PC are connected by 1000Base-T.

The readout PCs perform partial event building for data ransferred from the VME create. A data reduction of the partially built event is also performed in the readout PCs. It is important for the readout PCs to read out from the readout modules in such high rate of 30 kHz at this stage

The details of Stage1 are described in Chapter 4.

#### Stage2 (Distribution Stage)

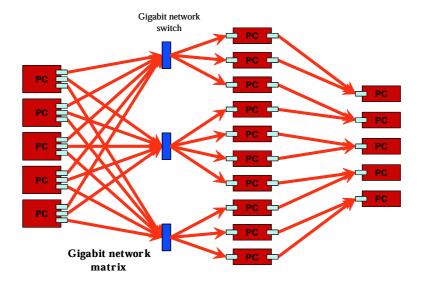

Stage indicates a network matrix for data transmission (distribution network matrix).

The readout PCs send the collected data from readout modules to one of *event-building* units. To distribute the collected data to *event building* unit, distribution network matrix

Figure 3.9: Global design of the event building farm for SuperKEKB

Figure 3.10: The schematic drawing of a part of Stage1. The black arrow is a data flow. Stage1 consists of the readout modules (COPPER boards), a gigabit network switch and a readout PC.

is constructed between the readout PCs and the event building units. Figure 3.11 shows the overview of Stage2 and the connections between them. We plan to employ about 10 event-building units at the beginning of SuperKEKB experiment. We can easily add more event building units to deal the increase of luminosity at SuperKEKB. The event fragments from sub-detectors are sent to one of the event building units. We can disperse the CPU usage of one event building unit, thus, the system can be scalable to handle the luminosity increase. Each of the readout PCs and event building units are connected by 1000Base-T via a network switch.

The details of Stage 2 are described in Chapter 5.

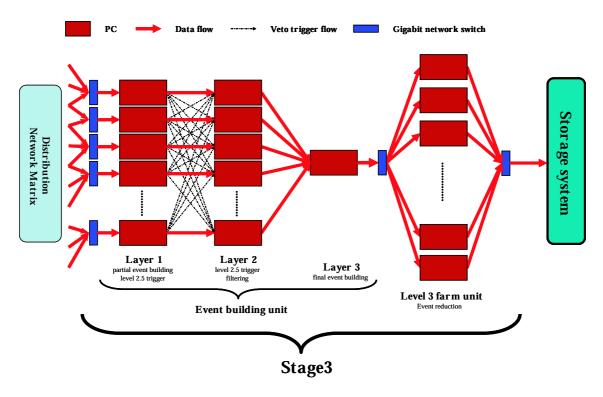

#### Stage3 (Full Event Building Stage)

Stage3 indicates the multiple unit array, which consists of the event building farm unit and level-3 trigger farm unit. Each event building unit in Stage3 has almost the same structure as the one used in the Belle DAQ system consisting of three layers of PC arrays. Figure 3.12 shows the overview of Stage3. In the first layer-PCs of an event building unit, all of the event fragments from one sub-detector are gathered, and a software trigger (level-2.5 trigger) processing is performed. In current Belle experiment, a fast track trigger using CDC information combine with the hardware trigger information is running as the level-2.5 trigger. Our software framework [16] is designed to work for run equally in both online and offline environment so that the software trigger for online processing can be developed easily using offline PCs. When one of the first-layer PCs fires an event rejection signal from level-2.5 trigger, it is sent to all second-layer PCs so that the whole event data is discarded in the second layer.

The final event building is performed in the third-layer PC in the event building unit.

Figure 3.11: The overview of Stage 2. Stage 2 consists of the readout PCs, the distribution network matrix and the layer-1 servers in the event building units.

A fully built event is then sent to a level-3 trigger farm, which is directly connected to the output from the third-layer PCs. A full event reconstruction is performed in the level-3 trigger farm unit and then a sophisticated event selection is performed. The selected events are finally sent to the data storage system.

We set up a proto-type event building farm with the design concept discussed in this section. We study the performance of Stage1 and Stage2 in the new DAQ system for the SuperKEKB experiment using the prototype event building farm. The results are discussed in the following two chapters.

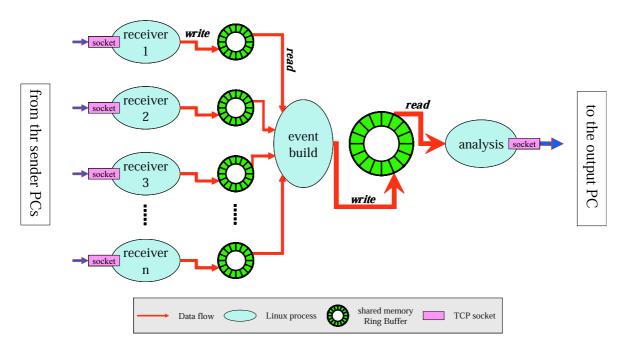

#### 3.3.2 Software Architecture

We develop the software to receive the event fragments from the many connections and perform the event building. The software structure in the readout PC is schematically drawn in Fig.3.13. An ellipse, a circle and an arrow indicate a Linux process, a shared memory and a data flow, respectively.

The data transfer is based on the TCP/IP (Transmission Control Protocol/Internet Protocol) to guarantee the reachability to the next PC and the ordering of the data fragments. The data from each sender PC are received at a TCP socket through network interface card (NIC) by one receiver process and stored in a shared memory buffer. The data are not merged at this moment. The event build process collects the data fragments from all shared memory buffers and builds the data record. The built data record is stored

Figure 3.12: The schematic drawing of one event building unit and one level-3 farm units

Figure 3.13: The software architecture for event building in the readout PC in case that n-th sender PC are connected.

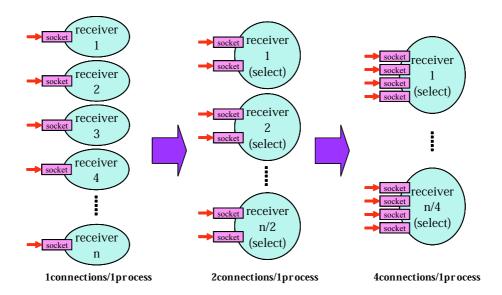

in another shared memory. The built data is read by the *analysis process* and is sent to the output PC. In real situation, we can process the built data record to reduce the data size. The number of receiver processes equals to the number of sender PCs. When the number of the sender PCs is "n", the total number of processes is "n + 2"; n receiver processes, one event build process and one analysis process.

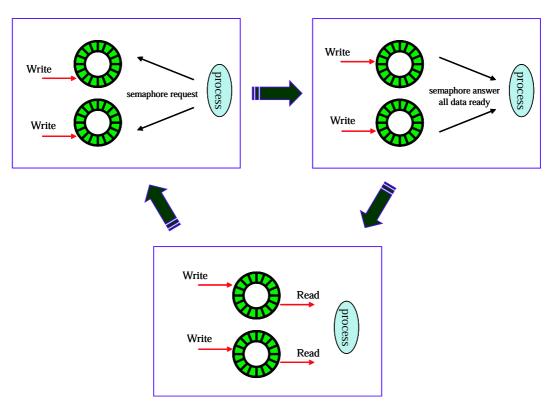

#### Ring Buffers of the Shared Memory

The shared memory buffer forms a ring buffer, which is divided into fixed size segments. This ring buffer can hold data up to 1000 event so that the receiver process can receive data from sender PCs as much as possible. We use SystemV semaphore to synchronize the received data fragments. The number of the stored event fragments and the number of empty segments in the ring buffer are recorded in the semaphore.

Figure 3.14: The schematic drawing of how the ring buffer works when the number of ring buffers is two.

Figure 3.14 shows how the ring buffer works. A Linux process asks the semaphore if data with a specific event number is available or not. When all event fragments belonging to the same event number are ready in the ring buffer, the Linux process accepts the reply from the semaphore and read the data from all shared memory buffers.

By changing the number of connections and the depth of the sheard memory, we can use this software at every Stage of the event building farm.

# Chapter 4

# Performance Study of Stage1 Event Building

To avoid the network congestion, all PCs of the event building farm are connected each other via point-to-point connections in the current Belle system. However the number of readout modules is considered to increase to more than 1000. To ease the maintenance and to reduce the cost and space, we need to keep the number of the readout PCs to be as small as possible. We then employ the small network switches in Stage1 of the event building farm for SuperKEKB. By using the network switch, we can reduce the number of network interface cards and the number of readout PCs, which gather the event fragments and performs the partial event building. We have to make sure that the network switch does not restrict the network flow and cause the network congestion. To decide the configuration of Stage1, we study the performance, which one readout PC collects the event fragments from many readout modules assuming the maximum number of 20. This chapter describe the performance studies of Stage1.

## 4.1 Basic Network Performance Study

In order to compare the readout network using the network switches (the network switch mode) with the one using the point-to-point connections (the point-to-point mode) and prove that the network switch is not the bottleneck of data transmission, we measure the event rate and the data transfer rate varying a event size. We also vary the number of PCs from one to eleven, which create the pseudo data and send it to one readout PC. We use PCs to simulate the readout modules described in the Subsection 3.2.4 and call them "sender PCs." In the network switch mode, each of the sender PCs and the readout PC is connected via the network switch. In the point-to-point mode, each of the sender PCs is connected directly with the readout PC and the network switch is not used. The readout PC does not build the received data so as to make no CPU usage except the data receiving process in the readout PC.

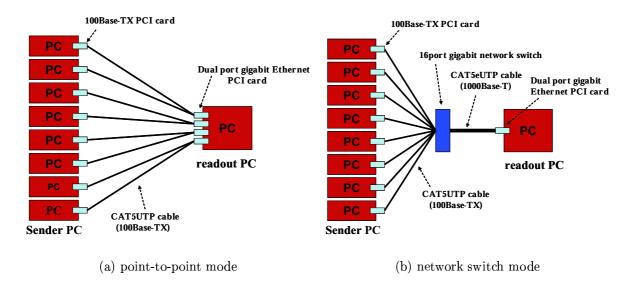

#### 4.1.1 Setup for Basic Network Performance Study

Test configuration of the point-to-point mode is shown in Fig.4.1(a). Each of sender PCs and the readout PC are connected directly via 100Base-TX with a CAT5 UTP cable. Test configuration of the network switch mode is shown in Fig.4.1(b). The sender PCs and the network switch are connected via 100Base-TX. The network switch and the readout PC are connected via 1000Base-T with a CAT5e UTP cable. The network switch is used to combine the 100Base-TX data flow into the flow of 1000Base-T. The switch we used is FXG-16TX, which is produced by PLANEX. It has 16 gigabit ports and 272 kB packet buffer memory. The transfer mode of this switch is the store&forward mode. The switch is also equipped with flow control, which employs IEEE802.3x in full duplex mode.

We use PCs, in which Red-Hat9 with 2.4.20-8smp kernel are installed, instead of a readout modules. The readout PC is equipped with two Intel Xeon CPUs operating at 2.46 GHz and Red-Hat9 with 2.4.20-8smp kernel is also installed. The CPUs of the readout PC are operated with Hyper Threading Technology enabled. Figure 4.2 shows the picture of the network switch and the readout PC.

Figure 4.1: The schematic drawings of the test configuration to study basic network performance.

# 4.1.2 Comparison of Network Switch Mode with Point-to-point Mode

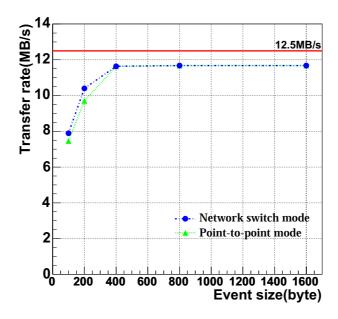

We measure the transfer rate of sender PC varying the event size per event. The result of the comparison of the network switch mode with the point-to-point mode is shown in Fig.4.3, when the number of sender PCs is eight.

We observe that the transfer rate of the both modes reaches close to the maximum transfer rate of 100Base-TX. When the event size is less than a few hundred bytes, the transfer rate of the network switch mode is 10 % higher than that of the point-to-point

Figure 4.2: The picture of the network switch (upper) and the readout PC (lower).

Figure 4.3: Comparison of the transfer rate of the network switch mode (blue) and that of the point-to-point mode (green) when the number of sender PCs is eight. The vertical axis shows the transfer rate and the horizontal axis shows the event size per sender PC. The horizontal solid line (red) is the maximum transfer rate of 100Base-TX (12.5 MB/s).

mode since the network switch has the packet buffer of 272 kB. We find that the network congestion does not occur in the network switch mode in the configuration of the number of sender PCs to be eight.

## 4.1.3 Number of Connections vs. Throughput

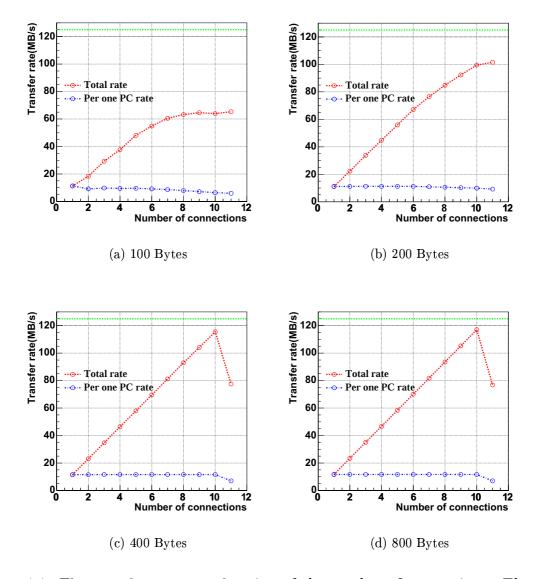

We measure the transfer rate varying the number of sender PCs from one to eleven and varying the event size from 100 to 800 Bytes. The results of the transfer rate measurement are shown in Fig.4.4.

Figure 4.4: The transfer rate as a function of the number of connections. The dashed (red) lines and the dotted (blue) lines show the total transfer rate and the transfer rate per sender PC, respectively. The green lines show the maximum transfer rate of 1000Base-T.

For the case of the event size of 100 and 200 Bytes, the total transfer rate is saturated at around eight or ten connections, respectively. The transfer rate per one sender PC slightly decreases. When the event size is 400 or 800 Bytes, the transfer rate per one sender PC reaches close to the limit of 100Base-TX), and the total transfer rate also reaches close to the limit of 1000Base-T at ten connections. In case of eleven connections, the total transfer rate and the single transfer rate drop to about 80 MB/s and about 7 MB/s in the 400 and 800 Bytes cases, respectively. This drop in data transfer rates indicates that the buffer memory of the network switch almost fulls since the connection between the network switch and the readout PC is over 1000Base-T (125 MB/s).

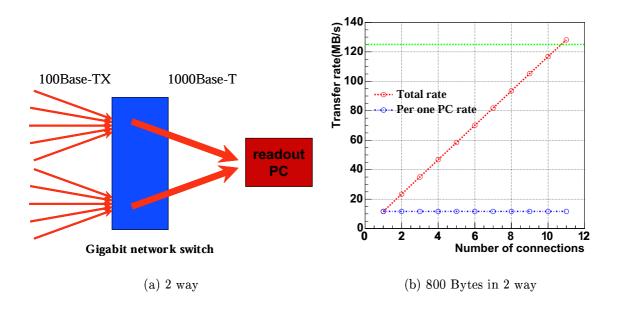

Figure 4.5: (a) The schematic drawing of data flow in network switch using two ports for output. (b) The transfer rate as a function of the number of connections. The dashed (red) line and the dotted (blue) line shows the total transfer rate and the transfer rate per Sender PC, respectively. The green line shows the maximum transfer rate of 1000Base-T (125 MB/s).

In order to solve the transfer rate drop at eleven connections, we use two ports to output the data (see Fig 4.5(a)). Figure 4.5(b) shows the result of the measurement using two ports for output. At the eleven connections, the total transfer rate exceeds the 1000Base-T capability and the single transfer rate does not drop in 100Base-TX since a load of data flow on one port of the network switch is dispersed. These two output data flows are independent of each other. By using the two ports for output, we can use full performance of the 1000Base-T even the number of connections is more than ten.

## 4.2 Performance of Stage1

In Stage1, the readout PC collects the digitized event fragments by the readout modules and performs the partial event building as described in Subsection 3.3.1.

Here, we summarize the requirements for Stage1.

- ♦ The readout PC should collect the event fragments from as many readout modules as possible to reduce the number of the readout PC. The maximum number of readout modules we consider is 20 modules.

- ♦ The readout PC should perform the partial event building in the high trigger rate of SuperKEKB. The typical trigger rate and the maximum trigger rate are considered to be 10 and 30 kHz, respectively.

#### 4.2.1 Test Setup

To investigate the performance of Stage1, we set up the test bench as shown in Fig.4.6.

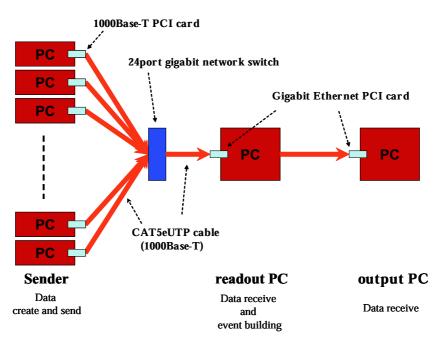

Figure 4.6: The test bench setup for Stage 1. The red arrows show the data flow.

The test bench consists of sender PCs, which can simulate the readout modules, the readout PC and the output PC. A role of each PC is as follows as:

- The sender PC emulate the readout module, generate a pseudo data and send them to the readout PC.

- The readout PC receive the pseudo data, build up one event and send the built data to the output PC.

- The output PC receive the built data.

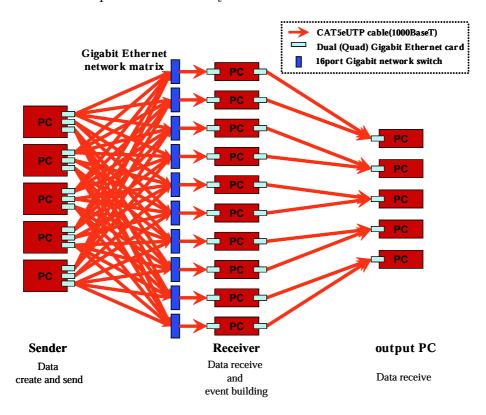

The pseudo data, which are generated by the sender PCs, are collected and built up into a single event by the readout PC. The readout PC sends the built data to the output PC. Each of the sender PCs and the readout PC is connected with the 1000Base-T Ethernet via a gigabit network switch. We use 24 port gigabit network switch, which is FMG-24K provided by PLANEX in this study. The transfer mode of the switch is the store&forward mode. The packet buffer memory in the network switch is 1 MB. In the real situation, the connection between the readout modules and the readout PC is 100Base-TX. If a throughput from the sender PCs to the readout PC is larger than 12.5 MB/s (the limit by 100Base-TX) in this study, the throughput should be considered to saturate at 12.5 MB/s in the real situation. The readout PC and the output PC are directly connected with the 1000Base-T Ethernet using point-to-point mode. Each of all PCs is a SMP server equipped with two Intel Xeon CPUs operating 3.06 GHz with Hyper Threading enabled and Red-Hat9 with 2.4.20-8smp kernel is installed. We use the event building software as shown in Fig.3.13.

#### 4.2.2 Results of Performance Measurement of Stage1

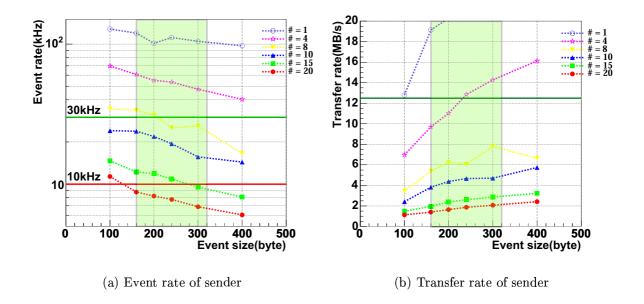

We study the performance of Stage1 varying the event size from 100 Bytes to 400 Bytes and the number of the sender PCs from one to twenty. The measured performances are the event rate and the transfer rate of the sender PCs. We define the event rate as the number of average events, which the sender PC has sent in every one second. Each sender PC sends the data to the readout PC as much as possible. So, the event rate indicates the upper limit of an acceptable trigger rate in Stage1.

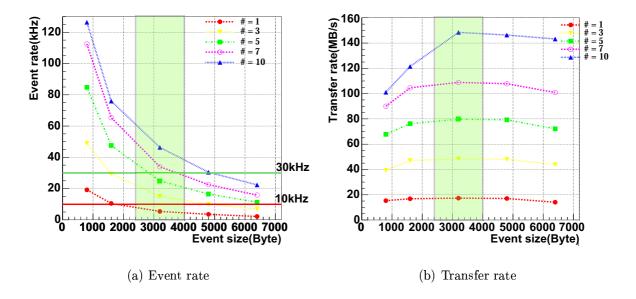

Figure 4.7 shows the results of Stage1 performances as a function of the event size. We also define the typical event size corresponding to the one from the drift chamber with 10 % occupancy. One channel of the drift chamber corresponds to 16 bytes. The number of channels of one readout module is assumed to be 100. One event size from one readout module is 1600 Bytes. When an occupancy of the drift chamber is 10 %, the typical event size becomes 160 Bytes. As shown in Fig 4.7(a), the event rate decreases by increasing the number of the sender PCs and reaches the typical trigger rate of 10 kHz when the number of the sender PCs is less than 15. The event rate also decreases by increasing the event size. As shown in Fig.4.7(b), if the number of the sender PCs is four, the transfer rate is to be over 12.5 MB/s at the event size of 240 Bytes. In the real situation, we use 100Base-T in the connection between each of the sender PCs and the readout PC, and this transfer rate saturates at 12.5 MB/s. The transfer rate increases according to the increase of the event size as shown in Fig.4.7(b).

#### Search for Bottleneck

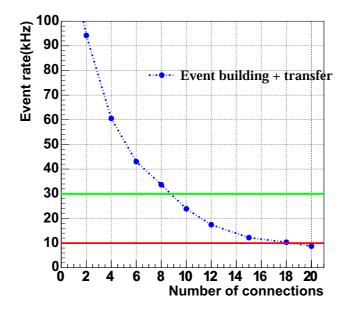

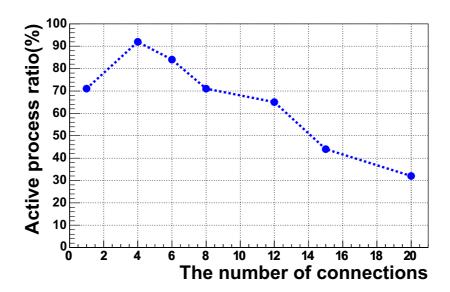

Figure 4.8 shows the event rate as a function of the number of the sender PCs at the typical event size of 160 Bytes. With the typical event size of 160 Bytes, the event rate reaches about 30 kHz when the number of sender PCs is less than eight. We find that the event rate decreases gradually as the number of the sender PCs increases. When the number of sender is 20, the event rate is about 8 kHz, which is not reached the typical trigger rate.

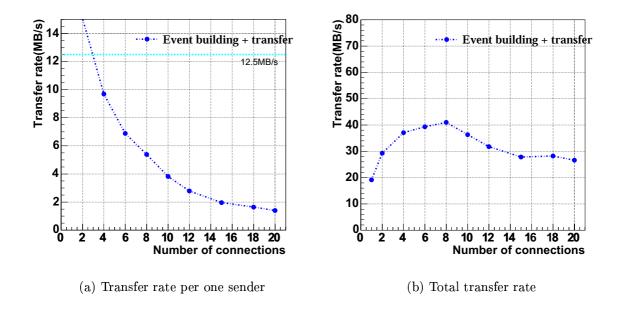

Figure 4.9 shows the transfer rate per one sender PC and total transfer rate. As shown

Figure 4.7: The result of the performance study of Stage1 for variable number of sender PCs. The horizontal axis shows the event size. The vertical axis shows the event rate (a) and the transfer rate (b), respectively. (a): The red horizontal line is the typical trigger rate. The green horizontal line is the maximum trigger rate of 30 kHz. (b): The horizontal green line is the limit of 100Base-TX. The light green area shows typical event size area where the occupancy of the drift chamber is assumed 10~% - 20~%