# Research and Development of Readout System for New Wide-Field CCD Camera of Subaru Telescope

Hironao Miyatake Department of Physics, University of Tokyo

January 2009

#### Abstract

The Hyper Suprime-Cam (HSC) is the next generation wide-field camera proposed for the 8.2-m diameter Subaru Telescope operated by the National Astronomical Observatory of Japan. One of the main purposes of the HSC is to put a new constraint on the nature of dark energy through weak lensing survey.

The HSC employs ~ 110 2kx4k Charge Coupled Devices (CCDs) to cover a 1.5 degree diameter field of view. The readout electronics is required to send ~ 2.1Gbytes of image data to downstream within 10 seconds. The noise from the readout system should be lower than that from the CCD, which is expected to be ~ 4e<sup>-</sup>. The readout system should be physically small and lightweight in order for it to be able to be mounted inside the camera unit.

We have developed a prototype readout module for the Back-End Electronics (BEE) of the readout system. The BEE is a digital component of the readout system, which provides an interface between an analog front end and a data acquisition system (DAQ system). Two Gigabit Ethernet links are employed for data transfer between the BEE and DAQ system in order to satisfy the data transfer rate requirement. The size of our BEE module is 149mm x 79mm x 12mm. We measured the performance of the BEE module. The data rate from the BEE module to the DAQ system reached full Gigabit Ethernet bandwidth and the noise induced by the BEE module is estimated to be  $\sim 0.05e^{-}$ .

We have built the prototype readout system using the BEE module and the analog front end of the existing wide-field camera of the Subaru Telescope. Using this system, we predicted the behavior of the readout system for the HSC. This demonstrates the feasibility of the HSC readout system using our BEE module.

# Contents

| 1        | Intr         | oducti                                                                                           | on                                                                                                                                              | 6                                                              |

|----------|--------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| <b>2</b> | Dar          | k Enei                                                                                           | gy and the Hyper Suprime-Cam                                                                                                                    | 8                                                              |

|          | 2.1          | Basics                                                                                           | of Cosmology and Dark Energy                                                                                                                    | 8                                                              |

|          | 2.2          | Weak                                                                                             | Lensing Survey                                                                                                                                  | 10                                                             |

|          |              | 2.2.1                                                                                            | Basic of Weak Lensing                                                                                                                           | 10                                                             |

|          |              | 2.2.2                                                                                            | Weak Lensing as a Probe of Dark Energy                                                                                                          | 12                                                             |

|          | 2.3          | Subar                                                                                            | 1 Telescope and Hyper Suprime-Cam                                                                                                               | 14                                                             |

|          |              | 2.3.1                                                                                            | Subaru Telescope                                                                                                                                | 15                                                             |

|          |              | 2.3.2                                                                                            | Overview of Hyper Suprime-Cam                                                                                                                   | 16                                                             |

|          |              | 2.3.3                                                                                            | Comparison with other projects                                                                                                                  | 19                                                             |

| 3        | Ove          | erview                                                                                           | of the Readout System for the Hyper Suprime-Cam                                                                                                 | 20                                                             |

|          | 3.1          |                                                                                                  | $ Concept \ldots \ldots$ | 20                                                             |

|          | 3.2          |                                                                                                  | End Electronics                                                                                                                                 | 22                                                             |

|          | 3.3          | Back I                                                                                           | End Electronics                                                                                                                                 | 23                                                             |

|          | <b>D</b> 0   | D (                                                                                              |                                                                                                                                                 | •                                                              |

| 4        |              |                                                                                                  | the Readout Module for the Back End Electronics                                                                                                 | <b>26</b>                                                      |

|          |              |                                                                                                  |                                                                                                                                                 | 2.0                                                            |

|          | 4.1          | -                                                                                                | rement                                                                                                                                          |                                                                |

|          | $4.1 \\ 4.2$ | Overv                                                                                            | $iew of the readout module \dots \dots$   | 27                                                             |

|          |              | Overvi<br>4.2.1                                                                                  | iew of the readout module                                                                                                                       | 27<br>27                                                       |

|          |              | Overvi<br>4.2.1<br>4.2.2                                                                         | iew of the readout module                                                                                                                       | 27<br>27<br>29                                                 |

|          | 4.2          | Overvi<br>4.2.1<br>4.2.2<br>4.2.3                                                                | iew of the readout module                                                                                                                       | 27<br>27<br>29<br>29                                           |

|          |              | Overvi<br>4.2.1<br>4.2.2<br>4.2.3<br>FPGA                                                        | iew of the readout module                                                                                                                       | 27<br>27<br>29<br>29<br>32                                     |

|          | 4.2          | Overvi<br>4.2.1<br>4.2.2<br>4.2.3<br>FPGA<br>4.3.1                                               | iew of the readout module                                                                                                                       | 27<br>27<br>29<br>29<br>32<br>32                               |

|          | 4.2          | Overvi<br>4.2.1<br>4.2.2<br>4.2.3<br>FPGA<br>4.3.1<br>4.3.2                                      | iew of the readout module                                                                                                                       | 27<br>27<br>29<br>29<br>32<br>32<br>32<br>34                   |

|          | 4.2          | Overvi<br>4.2.1<br>4.2.2<br>4.2.3<br>FPGA<br>4.3.1<br>4.3.2<br>4.3.3                             | iew of the readout module                                                                                                                       | 27<br>27<br>29<br>29<br>32<br>32<br>34<br>34                   |

|          | 4.2          | Overvi<br>4.2.1<br>4.2.2<br>4.2.3<br>FPGA<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                    | iew of the readout module                                                                                                                       | 27<br>27<br>29<br>29<br>32<br>32<br>34<br>34<br>41             |

|          | 4.2          | Overvi<br>4.2.1<br>4.2.2<br>4.2.3<br>FPGA<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Perfor          | iew of the readout module                                                                                                                       | 27<br>27<br>29<br>32<br>32<br>34<br>34<br>41<br>53             |

|          | 4.2          | Overvi<br>4.2.1<br>4.2.2<br>4.2.3<br>FPGA<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Perfor<br>4.4.1 | iew of the readout module                                                                                                                       | 27<br>27<br>29<br>32<br>32<br>34<br>34<br>41<br>53<br>53       |

|          | 4.2          | Overvi<br>4.2.1<br>4.2.2<br>4.2.3<br>FPGA<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Perfor          | iew of the readout module                                                                                                                       | 27<br>27<br>29<br>32<br>32<br>34<br>34<br>41<br>53<br>53<br>57 |

| <b>5</b>     | Pro | totype  | Readout System for Hyper Suprime-Cam    | 62 |

|--------------|-----|---------|-----------------------------------------|----|

|              | 5.1 | Protot  | ype Readout System                      | 62 |

|              | 5.2 | Perform | mance of Prototype Readout System       | 65 |

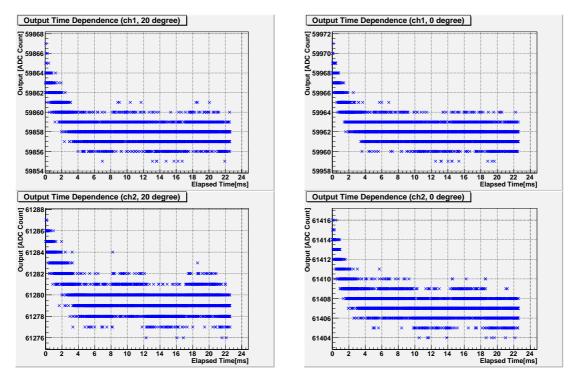

|              |     | 5.2.1   | Time Dependence of an output of the FEE | 65 |

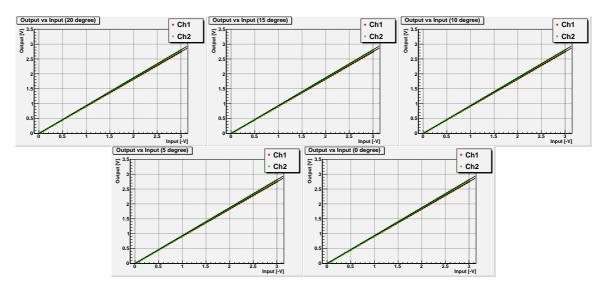

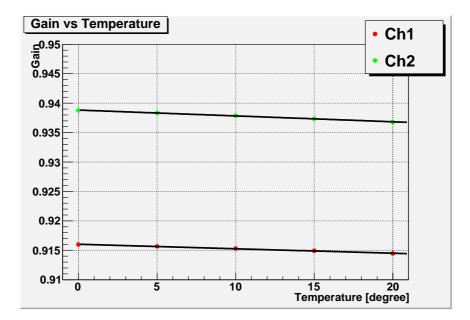

|              |     | 5.2.2   | Temperature Drift of CDS's gain         | 66 |

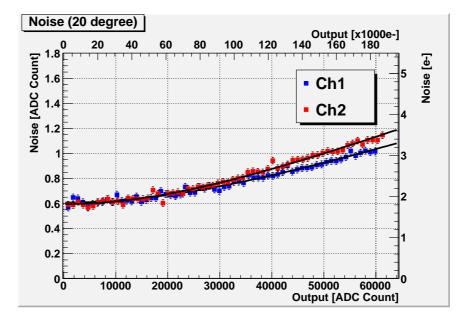

|              |     | 5.2.3   | Noise at fixed temperatures             | 70 |

| 6            | Con | clusior | 1                                       | 73 |

|              | 6.1 | Summa   | ary                                     | 73 |

|              | 6.2 | Future  | Prospect                                | 73 |

| $\mathbf{A}$ | Det | ails of | UDP Communication with GESiCA           | 75 |

|              | A.1 | RBCP    |                                         | 75 |

|              | A.2 | RBCP    | Communication with GESiCA               | 77 |

# List of Figures

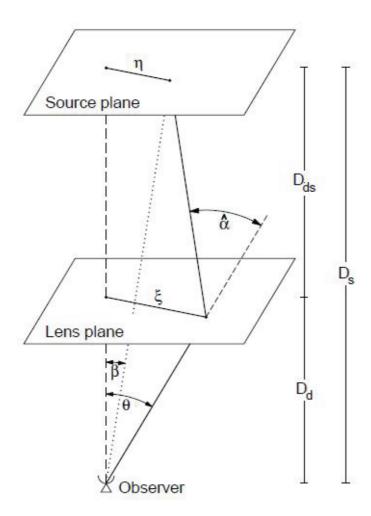

| 2.1     | Light Deflection by Gravitational Lens                                                   | 11              |

|---------|------------------------------------------------------------------------------------------|-----------------|

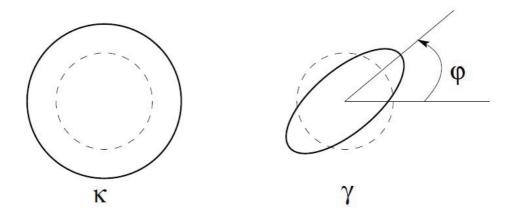

| 2.2     | Effect of Weak Lensing                                                                   | 13              |

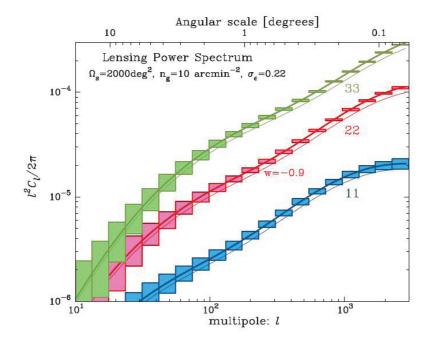

| 2.3     | Cosmic Shear Power Spectra Divided in Three Redshift Slices                              | 14              |

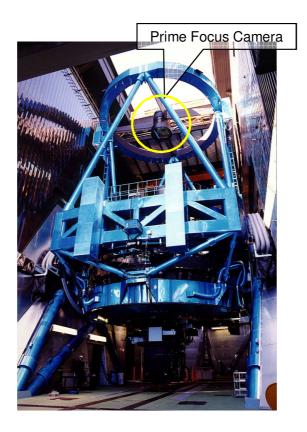

| 2.4     | Position of Prime Focus Camera                                                           | 15              |

| 2.5     | Structure of the Hyper Suprime-Cam                                                       | 16              |

| 2.6     | HSC CCD Alignment                                                                        | 17              |

| 2.7     | FDCCD                                                                                    | 18              |

| 3.1     | A schematic of the readout system for the HSC                                            | 21              |

| 3.2     | Correlated Double Sampling of CCD Signal. In a typical CCD signal, the                   |                 |

|         | reset part (corresponding to $0e^-$ ) comes first, and data part (corresponding          |                 |

|         | to the number of electrons which pixel acquired) next. The issue is that                 |                 |

|         | there is noise that adds the bias to the whole signal of one pixel, which is             |                 |

|         | called $kTC$ noise. To cancel this noise, the reset part and the data part are           |                 |

|         | integrated respectively and their difference is output. This process is called           | 00              |

| <u></u> | correlated double sampling                                                               | 22              |

| 3.3     | FEE Boards Alignment. The FEE boards are located under the cold plate<br>in the cryostat | 23              |

| 3.4     | Schematics of a planned BEE system                                                       | $\frac{23}{24}$ |

| 3.4     | Schematics of a planned BEE system                                                       | 24              |

| 4.1     | Photograph of prototype readout module (GESiCA) (front view) $\ldots$ .                  | 28              |

| 4.2     | Photograph of prototype readout module (GESiCA) (top view)                               | 28              |

| 4.3     | A block diagram of GESiCA                                                                | 31              |

| 4.4     | Image Data Header Specification. The size of the header is 32 bytes                      | 31              |

| 4.5     | Clock Distribution in FPGA                                                               | 33              |

| 4.6     | I/O of SiTCP                                                                             | 35              |

| 4.7     | Architecture of the Readout Controller.                                                  | 39              |

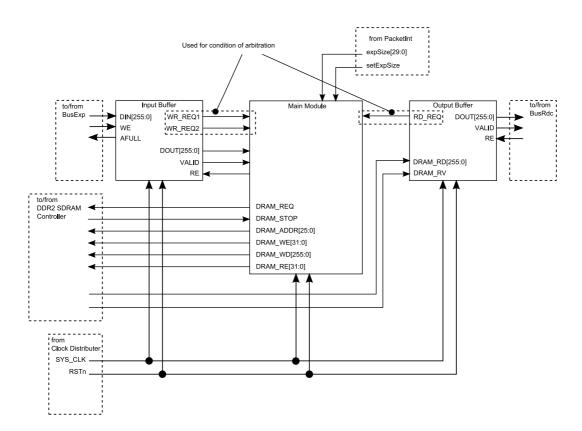

| 4.8     | I/O of the Frame Memory Controller                                                       | 42              |

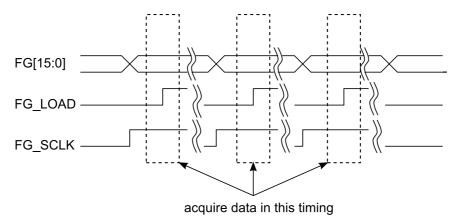

| 4.9     | Timing Chart of the Signal from the FEE                                                  | 43              |

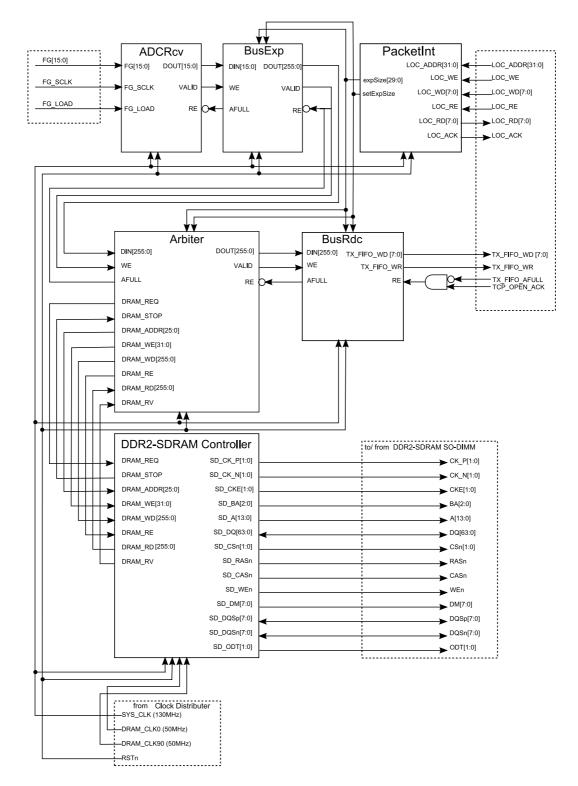

| 4.10    | Schematic of Frame Memory Controller                                                     | 44              |

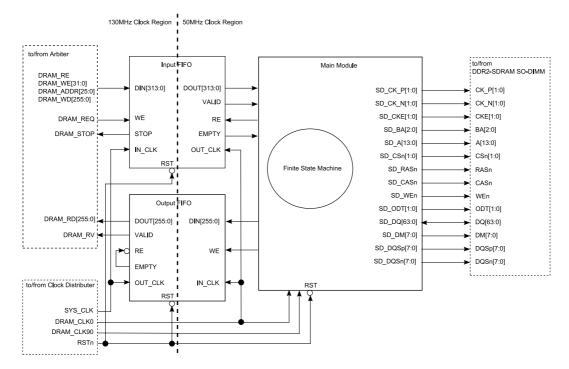

| 4.11    | Architecture of the DDR2 SDRAM controller                                                | 46              |

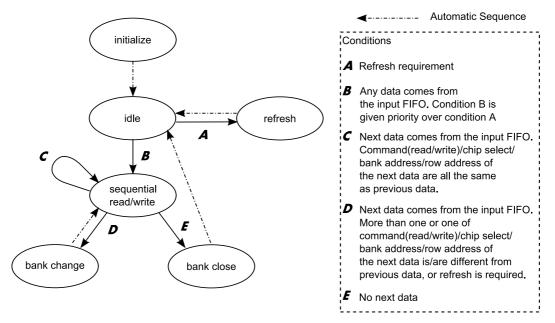

|         | State Transition Diagram of the DDR2 SDRAM controller                                    | 47              |

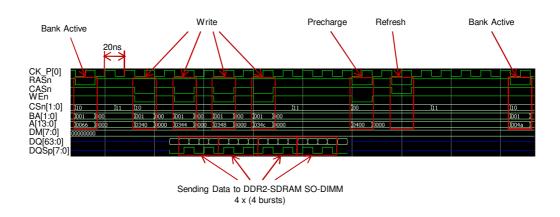

|         | Timing Chart of Sequential Write                                                         | 48              |

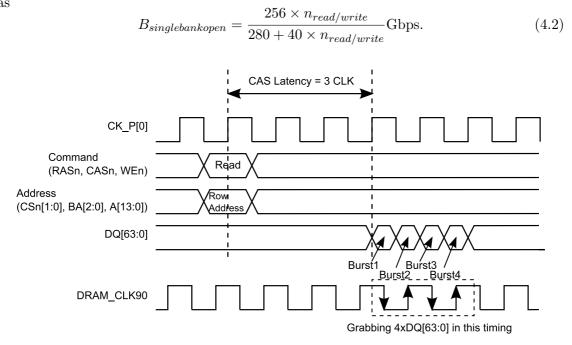

| 4.14    | Timing Chart of Read                                                                     | 49              |

|      | Architecture of the Arbiter                                               | 50 |

|------|---------------------------------------------------------------------------|----|

| 4.16 | An Example of Arbitration Timing                                          | 52 |

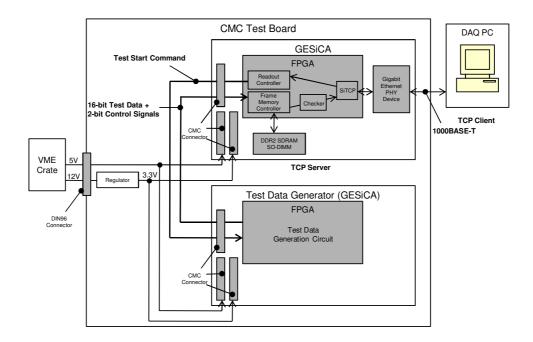

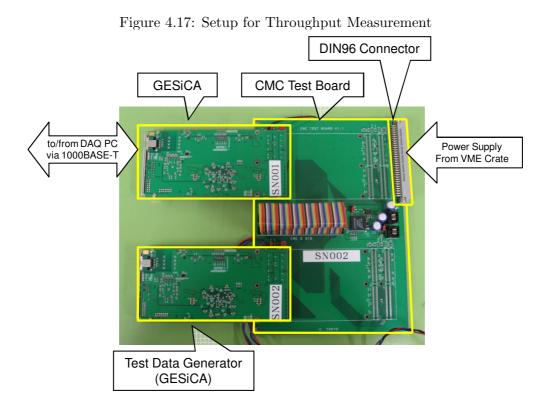

| 4.17 | Setup for Throughput Measurement                                          | 54 |

| 4.18 | Picture of Test System Used in Throughput Measurement                     | 54 |

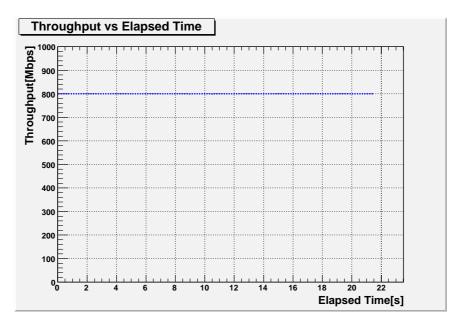

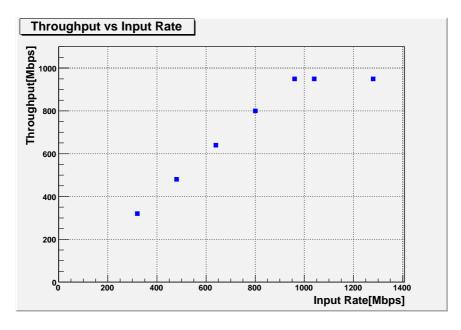

| 4.19 | Throughput Measurement: Throughput Time Dependence                        | 55 |

| 4.20 | Throughput Measurement: Throughput vs Input Rate                          | 56 |

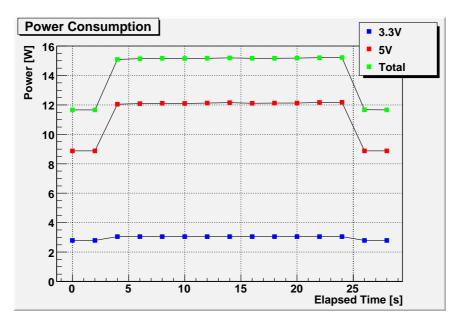

| 4.21 | Setup of Power Consumption Measurement                                    | 57 |

| 4.22 | Power Consumption Measurement                                             | 58 |

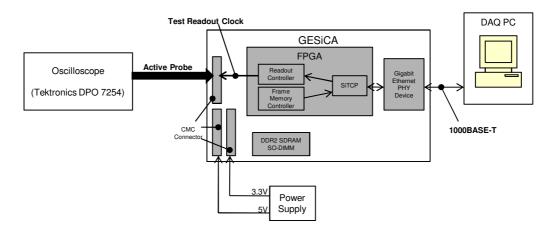

| 4.23 | Setup of the Jitter Measurement                                           | 59 |

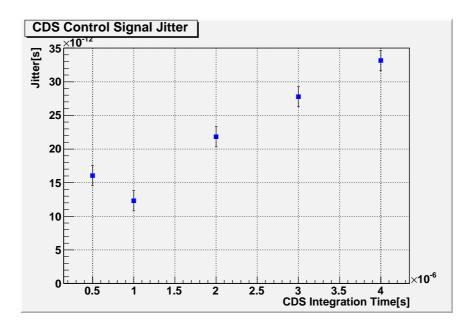

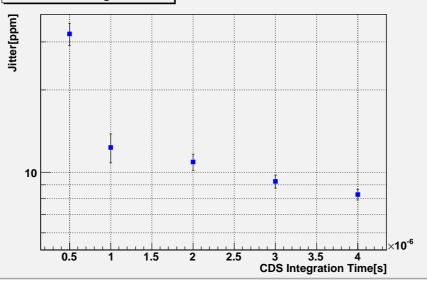

| 4.24 | Jitter Measurement of Readout Clock. Y-axis is the jitter in seconds      | 61 |

| 4.25 | Jitter Measurement of Readout Clock. Data is same as Fig.4.24, but Y-axis |    |

|      | is the relative accuracy in ppm                                           | 61 |

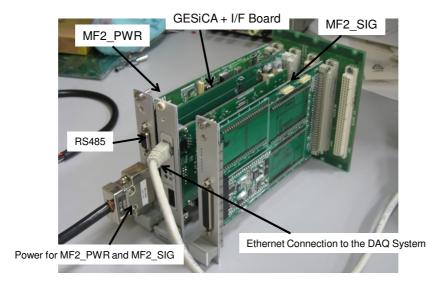

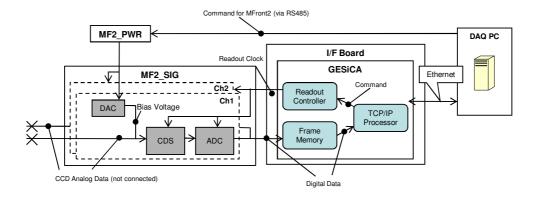

| 5.1  | Picture of the Prototype Readout System                                   | 63 |

| 5.2  | Schematic of Prototype Readout System                                     | 63 |

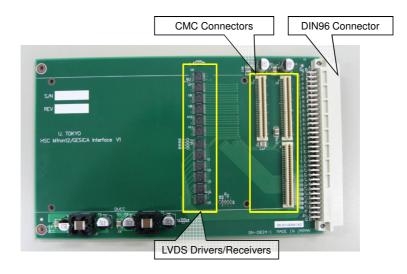

| 5.3  | Interface Board for GESiCA                                                | 64 |

| 5.4  | Output Time Dependence                                                    | 66 |

| 5.5  | Gain of the CDS                                                           | 67 |

| 5.6  | Temperature Drift of the Gain of the CDS                                  | 68 |

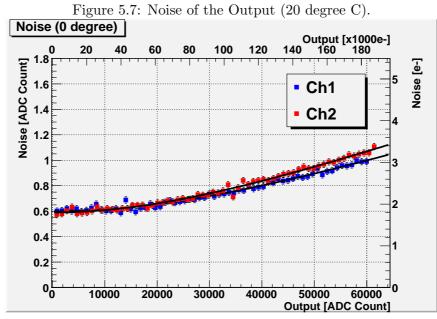

| 5.7  | Noise of the Output (20 degree C)                                         | 71 |

| 5.8  | Noise of the Output (0 degree C)                                          | 71 |

| A.1  | Schematic of communication over RBCP                                      | 75 |

| A.2  | RBCP Write Sequence                                                       |    |

|      | RBCP Read Sequence                                                        |    |

|      |                                                                           |    |

# List of Tables

| $2.1 \\ 2.2$ | FDCCD Specification. All parameters are measured in -100 degree Celsius .<br>Ongoing Projects for Probing Dark Energy                                                                                                                                                                                                                                                                                                                | $\frac{18}{19}$ |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 3.1          | Electronics Requirements                                                                                                                                                                                                                                                                                                                                                                                                             | 20              |

| 4.1          | Pin assignment of the CMC connector of GESiCA. PIN0-3/POUT0-3 are general purpose inputs/outputs. RESET is used for master reset. ACTIVE is used for return from sleep. SYNC0-1 are used for synchronization of readout modules. UART0-1 are used for serial communication. The signals mentioned above will be used in the future. FG_SCLK and FG_LOAD are the control signal from the FEE. FG0-15 is the 16-bit digital image data |                 |

|              | from the FEE. CP0-31 is the 32-bit readout clock for the CCDs and the FEE.                                                                                                                                                                                                                                                                                                                                                           | 30              |

| 4.2          | User Interface Signals of SiTCP                                                                                                                                                                                                                                                                                                                                                                                                      | 35              |

| 4.3          | Structure of the Memory of the Pattern Generator                                                                                                                                                                                                                                                                                                                                                                                     | 40              |

| 4.4          | Structure of the Memory in the Pattern Sequencer                                                                                                                                                                                                                                                                                                                                                                                     | 40              |

| 4.5          | DDR2 SDRAM Initialization Settings                                                                                                                                                                                                                                                                                                                                                                                                   | 48              |

| 5.1          | Gain of the CDS from the Fit                                                                                                                                                                                                                                                                                                                                                                                                         | 68              |

| 5.2          | Relative Temperature Drift                                                                                                                                                                                                                                                                                                                                                                                                           | 69              |

| 5.3          | Result of Fit                                                                                                                                                                                                                                                                                                                                                                                                                        | 72              |

| A.1          | Packet Format of RBCP                                                                                                                                                                                                                                                                                                                                                                                                                | 76              |

| A.2          | Address Map for GESiCA Control                                                                                                                                                                                                                                                                                                                                                                                                       | 80              |

| A.3          | Address Map for Each Octet of setExpSize Address                                                                                                                                                                                                                                                                                                                                                                                     | 80              |

| A.4          | Address Map for Each Octet of PtRAM Address                                                                                                                                                                                                                                                                                                                                                                                          | 80              |

| A.5          | Address Map for Each Octet of PrRAM Address                                                                                                                                                                                                                                                                                                                                                                                          | 80              |

# Chapter 1 Introduction

The drastic advancements in astronomical observation technology in the last decade has cast a profound issue straddling the line between particle physics and cosmology: dark energy, an unidentified energy that fills the entire space and increases the rate of expansion of the universe. In 1998, the observation of type Ia supernovae suggested that the expansion of the universe is accelerating[1]. The measurement of the cosmic microwave background (CMB) by the Wilkinson Microwave Anisotropy Probe (WMAP) has made a strong confirmation of the existence of dark energy[3]. According to the result from WMAP, the energy of the universe is made up of 72 % dark energy, 23 % dark matter, and 5 % of matter we already know (baryons). It is amazing that the main part of the universe is filled with such a peculiar energy.

On a superficial level, dark energy seems to be cosmological constant which Einstein introduced about nine decades ago. However, it constitutes a contradiction with particle physics; present particle physics cannot explain what field dark energy is. For instance, the natural value of the cosmological constant predicted by particle physics is  $\Lambda = c^2/(\hbar G) \sim$  $5.2 \times 10^{93}$  g/cm<sup>3</sup>, which results in  $\Omega_{de} \sim 10^{121}$ . On the other hand, as we mentioned above, observations report  $\Omega_{de} \sim 0.72$ . There is an order of  $10^{121}$  of discrepancy between the prediction and the observation, making it one of the worst predictions in history. In addition, dark energy may suggest a limitation of general relativity; general relativity may be no longer applicable on extremely large scales. There is a possibility that dark energy will fundamentally change our view of the world.

To obtain a hint to identify dark energy, it is important to investigate the nature of dark energy such as its time evolution. One of the most efficient methods to survey dark energy is to map a 3D distribution of mass using weak lensing. Many cosmological observations including galaxy surveys revealed that the universe has a vast hierarchy which results in concavity and convexity of space structure. According to Einstein's general relativity, the concavity and convexity of space curves light from distant galaxies. As a result, observers observe systematically distorted images of galaxies. This phenomenon is called cosmological weak lensing. Gravity caused by dark matter is crucial for forming the hierarchical structure of the universe. Dark energy also influences the hierarchy through the expansion of the universe. Therefore observations of the cosmological weak lensing will help us to understand the nature of dark energy. Measurements of weak lensing have an advantage in smaller systematic error compared with other measurements since there is no assumption of composition or state of matter. In addition, combining other independent methods (CMB, supernovae, and baryon acoustic oscillation) will give stringent constraints on the nature of dark energy.

It is crucial to take extremely high-resolution images of galaxies since cosmic weak lensing effect is very small (~1% in ellipticity). The existing prime focus camera mounted on Subaru Telescope, the Suprime-Cam, has an advantage in this regard since the Subaru Telescope has superb image resolution. However, the field of view of the Suprime-Cam is not large enough to measure the influence for weak lensing caused by dark energy. Therefore we are developing the new wide-field camera called Hyper Suprime-Cam (HSC)[9]. The field of view of the HSC is 1.5 degrees in diameter which is ~ 7 times larger than that of Suprime-Cam. Surveying 1000 square degrees of the sky (approximately one fortieth of whole sky), we aim to statistically impose stringent limitation on the nature of dark energy.

The HSC employs ~ 110 CCDs. The size of one exposure is ~2 Gbytes. The readout system for the HSC processes this large amount of data, which is then transferred to the data acquisition (DAQ) system. The requirement for readout time is that the readout system should send the whole image data of one exposure to the DAQ system within 10 seconds. The noise from the readout system should be smaller than that from the CCD (~4e<sup>-</sup>). The readout system should be small and light, and its power consumption should be low, because the readout system will be integrated in the camera unit.

Physical motivation and introduction to the HSC will be discussed in Chapter 2, and the overview of the readout system for the HSC will be discussed in Chapter 3. In Chapter 4, the main part of this thesis, we will describe the research and development of the readout module for the digital part of the readout system. In this chapter, the specification, architecture, and evaluation of this module will be discussed. We have built the prototype readout system which consists of the readout module we developed and the analog part of the Suprime-Cam. The evaluation of this system will be described in Chapter 5. We summarize our study in Chapter 6.

# Chapter 2

# Dark Energy and the Hyper Suprime-Cam

# 2.1 Basics of Cosmology and Dark Energy

Einstein's equation is written as

$$G_{\mu\nu} + \Lambda g_{\mu\nu} = \frac{8\pi G}{c^4} T_{\mu\nu}, \qquad (2.1)$$

where  $G_{\mu\nu}$  is the Einstein tensor,  $\Lambda$  is the cosmological constant,  $g_{\mu\nu}$  is the metric tensor, G is the gravitational constant, c is the speed of light, and  $T_{\mu\nu}$  is the stress-energy tensor. The left-hand side of equation (2.1) represents "geometry of space-time", while the right-hand side represents "distribution of matter field". Although they have apparently no relation to each other, Einstein's equation relates them: once one of them is determined, the other is automatically determined. The cosmological constant was originally introduced by Einstein in order to allow static cosmological solutions. The cosmological constant can be interpreted as a part of the stress-energy tensor which is inherent in space and independent of matter, when it is moved to the right-hand side;

$$G_{\mu\nu} = \frac{8\pi G}{c^4} (T_{\mu\nu} - \frac{c^4}{8\pi G} \Lambda g_{\mu\nu}).$$

(2.2)

If there was no matter in the universe, that is,  $T_{\mu\nu} = 0$ , the energy resulting from  $\Lambda$  would exist. In this sense, the second term of the right-hand side of the equation (2.2) is called "vacuum energy."

Let us postulate that the universe is *homogeneous* and *isotropic*. This postulate is called the cosmological principle. When the universe is isotropic, we can write an actual distance as

$$X(t) = a(t)x, \tag{2.3}$$

a(t) is called the scale factor whose present value is one. While a(t) changes with time, x is independent of time. x is called *comoving distance*. Since we have good evidence that the universe is expanding, a(t) was smaller than one at earlier times. We define *comoving coordinate* as the coordinate system where comoving distance is defined. Under the cosmological principle, the metric can be represented as

$$ds^{2} = -dt^{2} + a^{2}(t) \left[ \frac{dr^{2}}{1 - Kr^{2}} + r^{2}(d\theta + \sin^{2}\theta d\phi^{2}) \right],$$

(2.4)

where K is a curvature.  $r, \theta, \phi$  is the comoving coordinate of the spherical coordinate system. This metric is called Robertson-Walker metric.

The cosmological principle enable us to assume that the universe is filled with the a homogeneous perfect fluid which can be written as

$$T_{\mu\nu} = (\rho c^2 + P)u_{\mu}v_{\nu} + Pg_{\mu\nu}$$

(2.5)

in the form of the stress-energy tensor. Here  $\rho$  is the energy density, P is the pressure, and  $u_{\mu}$ ,  $v_{\nu}$  is the four-vector velocity.

Under the cosmological principle which corresponds to equations (2.4) and (2.5), Einstein's equation becomes

$$\left(\frac{\dot{a}}{a}\right)^2 = \frac{8\pi G\rho}{3} - \frac{Kc^2}{a^2} + \frac{\Lambda c^2}{3},$$

(2.6)

$$\frac{\ddot{a}}{a} = -\frac{4\pi G}{3c^2}(\rho c^2 + 3P) + \frac{\Lambda c^2}{3},$$

(2.7)

which is called Freedmann equations.

Let us assume that the relation between the energy density  $\rho$  and P has the form of

$$P = w\rho c^2. \tag{2.8}$$

This equation is called the equation of state. w = 0 for matter (non-relativistic particle) and w = 1/3 for radiation (relativistic particle). Therefore, due to equation (2.7), it turns out that matter and radiation make a contribution to the deacceleration of the universe's expansion ( $\ddot{a} < 0$ ). Vacuum energy makes a contribution to the acceleration of the expansion ( $\ddot{a} > 0$ ). As for vacuum energy equation of state, from equations (2.2) and (2.5) we can obtain

$$\rho_v = \frac{\Lambda c^2}{8\pi G}, P_v = -\frac{\Lambda c^4}{8\pi G}, \qquad (2.9)$$

which results in w = -1. Generally, the energy fluid which has w < -1/3 accelerates expansion of the universe. We call such energy "dark energy". In this sense, vacuum energy can be interpreted as a special form of dark energy. w may change with time. From now on, we generalize the vacuum energy as dark energy and write  $\rho_v$  and  $P_v$  as  $\rho_{de}$ and  $P_{de}$  which have the relation of  $P_{de} = w\rho_{de}c^2$ Using the Hubble parameter  $H = \dot{a}/a$  and  $\Omega = \rho/\rho_{cr,0}$  where the present critical

Using the Hubble parameter  $H = \dot{a}/a$  and  $\Omega = \rho/\rho_{cr,0}$  where the present critical density  $\rho_{cr,0} = \frac{3H_0^2}{8\pi G}$  and setting  $t = t_0$  (present), equation (2.6) becomes

$$1 = \Omega_{r,0} + \Omega_{m,0} + \Omega_{de,0} + \Omega_{K,0}, \qquad (2.10)$$

where  $\Omega_{K,0} = -K_0 c^2 / a^2 H_0^2$ . Thus energy of the universe is filled with radiation, matter, dark energy, and curvature.

Recent cosmological observations, including the observations of type Ia supernovae[1][2] and cosmic microwave background(CMB), strongly support the  $\Lambda$ CDM model.  $\Lambda$  stands for the cosmological constant (dark energy) that allows for the current accelerating expansion of the universe. CDM stands for cold dark matter; the matter that seldom interacts with others (i.e. dark matter is not baryons) and was cooled (i.e. its velocity is nonrelativistic) at the epoch of radiation-matter equality. Cold dark matter is necessary to realize the present structure of the universe. According to the  $\Lambda$ CDM model,  $\Omega_{r,0}$  in equation (2.10) = 0.

The cosmological parameters with 68% CL, derived from the Wilkinson Microwave Anisotropy Probe (WMAP) data combined with the type Ia supernova (SN) and baryon acoustic oscillation (BAO) under the  $\Lambda$ CDM model, are [3]:  $\Omega_{b,0} = 0.0456 \pm 0.0015$ ,  $\Omega_{dm,0} = 0.228 \pm 0.013$ ,  $\Omega_{de,0} = 0.726 \pm 0.015$ , where indices b and dm mean the baryon and the dark matter respectively. In addition, the limitations -0.14 < 1 + w < 0.12,  $-0.0179 < \Omega_{K,0} < 0.0081$  (95% CL) were obtained, where w is assumed to be constant. These results are consistent with equation 2.10, which supports inflation theory.

Weak lensing surveys are expected to tighten the limitation of the cosmological parameters described above, because they are an observation independent of the other methods. In the next section, we discuss the efficiency of weak lensing surveys.

# 2.2 Weak Lensing Survey

According to general relativity, mass structure induces distortion of space-time, which results in the deflection of light which go through space-time. Therefore observers observe distorted galaxy images. This is called weak lensing. The distortion is affected not only by matter but also dark energy, since dark energy influences the evolution of the universe through its "negative pressure." In this section we discuss basic of weak lensing and then how weak lensing is used as a probe of dark energy.

## 2.2.1 Basic of Weak Lensing

Fig. 2.1 shows the typical system of gravitational lensing, where a mass concentration at angular distance  $D_d$  deflects the light from a source at angular distance  $D_s$ , that is, the mass concentration behaves as a lens.  $D_{ds}$  is angular distance between the lens and the source. Deflected by the deflection angle  $\vec{\alpha}(\vec{\theta})$ , the true image at the position  $\vec{\beta}$  is observed at  $\vec{\theta}$ . Supposing all the angles are sufficiently small, the relation between these angles is written as

$$\vec{\beta} = \vec{\theta} - \frac{D_{ds}}{D_s} \vec{\hat{\alpha}}(\vec{\theta}) \equiv \vec{\theta} - \vec{\alpha}(\vec{\theta}), \qquad (2.11)$$

Figure 2.1: Light Deflection by Gravitational Lens

which is called the lens equation. We defined the scaled deflection angle  $\vec{\alpha}(\vec{\theta})$  in the last step. General relativity predicts the deflection angle  $\vec{\alpha}(\vec{\theta})$  is

$$\vec{\alpha}(\vec{\theta}) = \nabla \psi(\vec{\theta}) = \frac{4G}{c^2} \frac{D_s D_{ds}}{D_s} \int d^2 \vec{\theta'} \frac{\vec{\theta} - \vec{\theta'}}{|\vec{\theta} - \vec{\theta'}|^2} \Sigma(D_d \vec{\theta'}), \qquad (2.12)$$

where  $\Sigma$  is the 2-dimensional mass density on which mass density of lens objects is projected along the line of sight, represented as  $\Sigma(\vec{\theta}) = \int dz \rho(D_d \vec{\theta}, z)$ .  $\psi$  can be regarded as the bundle potential resulting from the mass structure.

Let us consider the gravitational lensing mapping which can be represented by equations (2.11) and (2.12). The small deviation  $(\delta \vec{\beta}, \delta \vec{\theta})$  which moves inside a galaxy image around the center of the galaxy  $(\vec{\beta}, \vec{\theta})$  is represented as

$$\delta\vec{\beta} = \frac{\partial\beta(\vec{\theta})}{\partial\vec{\theta}}\delta\vec{\theta} \equiv A(\vec{\theta})\delta\vec{\theta}, \qquad (2.13)$$

where

$$A = \left(\delta_{ij} - \frac{\partial^2 \psi(\vec{\theta})}{\partial \theta_i \partial \theta_j}\right) = \left(\begin{array}{cc} 1 - \kappa - \gamma_1 & -\gamma_2 \\ -\gamma_2 & 1 - \kappa + \gamma_1 \end{array}\right).$$

(2.14)

Here convergence  $\kappa$  and shear  $\gamma = \gamma_1 + i\gamma_2 = |\gamma|e^{2i\varphi}$  are

$$\kappa \equiv \frac{1}{2}(\psi_{11} + \psi_{22}),$$

(2.15)

$$\gamma_1 \equiv \frac{1}{2}(\psi_{11} - \psi_{22}),$$

(2.16)

$$\gamma_2 \equiv \psi_{12} \tag{2.17}$$

For the case of weak lensing, which we define by  $\kappa \ll 1$  and  $|\gamma| \ll 1$ , the transformation matrix A maps the intrinsic image  $\vec{\beta}$  into the distorted image  $\vec{\theta}$  like Fig. 2.2. We supposed the intrinsic image is a circle. Convergence  $\kappa$  increases the size of the image by  $1/(1-\kappa)$ , shown as the left of Fig. 2.2. Shear  $\gamma$  does not change the size but transforms the shape into ellipse (see the right of Fig. 2.2). The induced ellipticity is represented as  $e = (a - b)/(a + b) = |\gamma|$  (a, b is length of the major axis and that of the minor axis, respectively) and angle of direction of the major axis is  $\phi = (1/2) \arctan(\gamma_1/\gamma_2)$ .

## 2.2.2 Weak Lensing as a Probe of Dark Energy

Weak lensing due to cosmological large-scale structure, including dark energy, causes the distortion of distant galaxies which is called *cosmic shear*. The two-point correlation function of the cosmic shear,  $\langle \gamma(\vec{\theta_1})\gamma(\vec{\theta_2}) \rangle$ , is the powerful tool to examine our cosmological model. Since the shear signal due to dark energy is very weak (~ 1% in ellipticity), we have to minimize both statistical and systematic error.

We need to extract small cosmic shear signal from galaxies which have inherent ellipticity. Although the ellipticity magnitude of a galaxy is  $\sim 30\%$  in average, its direction is likely to be random. This fact implies that we can measure the cosmic shear by averaging

Figure 2.2: Effect of Weak Lensing

the distortions over a sufficiently large number of galaxies and cancelling their intrinsic ellipticity. Thus, the cosmic shear correlation function is an intrinsically statistical quantity. To reduce the statistical error, a large number of galaxies images are required.

Another key to extract the cosmic shear signal precisely is measuring shape of galaxies with a high degree of accuracy from contamination due to atmospheric seeing effect and telescope distortion. To this end, well-resolved and excellent image quality is required. As a measure of resolution, the Shear TEsting Programme (STEP), the project of simulation for cosmic shear measurement, reports image quality with seeing of ~ 0.6" (typical Subaru Telescope seeing) and pixel resolution of ~ 0.2" is good enough for precise measurement of the shear effect[8].

Power spectrum, the Fourier transformed counterpart of the cosmic shear correlation function, is estimated to depend roughly on the cosmological parameters from a perturbative calculation based on the  $\Lambda$ CDM model[7]:

$$P \propto \Omega_{DE}^{-3.5} \sigma_8^{2.9} z_s^{1.6} |w|^{0.31}, \qquad (2.18)$$

where  $\sigma_8$  is the mass dispersion on a scale of 8  $h^{-1}$ Mpc (h is defined as  $H_0 = 100h$  km s<sup>-1</sup> Mpc<sup>-1</sup>), and  $z_s$  is the redshift of the source galaxies and the dark energy equation state w is assumed to be constant. Equation (2.18) is the approximation around  $z_s = 1$  and multipoles l = 1000.

We must consider degeneracies between these cosmological parameters. One way to resolve the degeneracies is binning weak lensing by  $z_s$ . This method is called *weak lensing* tomography. The multi-color data set of the weak lensing survey can be used to estimate the distances of galaxies  $z_s$ , the so-called photo-z, by utilizing the fact that galaxies display characteristic photometric features depending on the redshift and type of galaxies. Weak lensing tomography is expected to impose tighter restrictions on the nature of dark energy[6].

Figure 2.3: Cosmic Shear Power Spectra Divided in Three Redshift Slices

Here we describe an example of applying weak lensing tomography for estimating cosmological parameters having a relation to dark energy. Fig. 2.3 shows the expected cosmic shear power spectra for galaxy distribution divided in three redshifts slices,  $0 \leq z_1 \leq 0.6$ ,  $0.6 \leq z_2 \leq 1$ ,  $z_3 \geq 1$ . The bold solid curves are power spectra for  $\Lambda$ CDM model, while the thin line curves show the results for a model with w = -0.9. The boxes around the bold lines are the expected measurement error for the weak lensing survey that is parametrized by survey area  $\Omega_s=2,000 \text{deg}^2$ , the average number density of galaxies usable for lensing analysis,  $\bar{n}_g=30 \text{arcmin}^{-2}$ , and the rms intrinsic ellipticities,  $\sigma_{\epsilon}=0.22$ . This figure shows the possibility of splitting degeneracies. For example, if  $\sigma_8$  is fixed by using the WMAP data, we can estimate not only  $\Omega_{de}$  and (constant) w, but also time dependency of w. These information will give us a significant clue to reveal the identity of dark energy.

# 2.3 Subaru Telescope and Hyper Suprime-Cam

The requirements for observation to extract the information of dark energy by weak lensing survey are

- 1. extremely wide-field survey, and

- 2. well-resolved and undistorted image.

We are developing the next generation wide-field camera satisfying above requirements, which will be mounted on Subaru Telescope. In this section, we discuss the Subaru Telescope, the new camera and comparison with other survey projects.

# 2.3.1 Subaru Telescope

Subaru Telescope is located at the 4,200-meter summit of Mauna Kea on the island of Hawaii, which commenced operation in 1999. The Subaru Telescope is operated by National Astronomical Observatory of Japan (NAOJ).

Figure 2.4: Position of Prime Focus Camera

The features of Subaru Telescope are as follows:

• 8.2-m large primary mirror

Subaru Telescope has a single 8.2-m large primary mirror which enables us to survey darker objects and the deeper field.

• prime focus

Generally, the larger primary mirror a telescope has, the smaller field of view (FOV) becomes. However, Subaru Telescope has prime focus where we can set a wide-field camera. This feature is unique among many telescopes in the world.

• high-quality imaging

Subaru Telescope has actuators under its 8.2-m primary mirror to compensate distortion of the mirror. This feature gives us extremely high-quality images.

Subaru Telescope currently mounts Suprime-Cam on its prime focus[10]. The FOV of Suprime-Cam is 0.34 degree  $\times$  0.27 degree. The Suprime-Cam has been providing un-vignetted, wide- and deep-field images. In fact, superb images better than 0.6 arcsec (FWHM) are routinely obtained by Suprime-Cam. Thanks to the Suprime-Cam, dark halos are observed by weak lensing survey[11]. In addition, cosmic shear statistics becomes possible, resulting in rejection of the cosmological model without cosmological constant[12].

## 2.3.2 Overview of Hyper Suprime-Cam

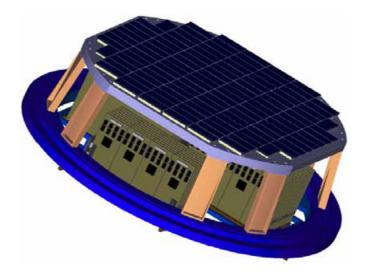

Although the Suprime-Cam provides high-quality and wide-field images, its FOV is not enough to survey dark energy. We are developing a new wide-field prime focus camera of Subaru Telescope, which is called Hyper Suprime-Cam (HSC), whose FOV is 1.5 degrees in diameter and first light on sky is scheduled on 2011. This wide field enables our survey speed to increase approximately 10 times faster than that of Suprime-cam.

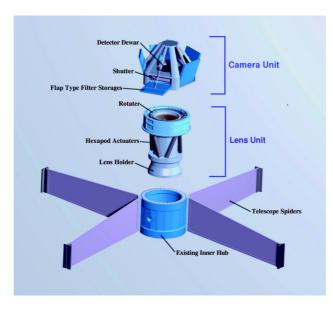

Figure 2.5: Structure of the Hyper Suprime-Cam

Fig. 2.5 shows the structure of the HSC. The structure consists of two units: a lens unit and a camera unit. The lens unit is attached to the telescope from zenith, and the lens barrel containing optics is supported by the hexapod actuators so that the attitude can be controlled. The camera unit is attached to the end of the lens barrel.

## Optics

The optical specification is represented as the 80 % encircled energy diameter,  $D_{80}$ . In the red band ( $\lambda > 600$  nm), where shape measurement of galaxies are usually carried out for weak lensing analysis,  $D_{80}$  should be equivalent with that of Suprime-Cam (~0.3 arcsec). For the blue region ~0.3 arcsec is goal. The optics satisfying this requirement is under development.

## CCD

HSC CCD alignment, pattern 2 (106 CCDs)

Figure 2.6: HSC CCD Alignment

We use ~ 110 CCDs to cover FOV of 1.5 degree diameter as shown in Fig. 2.6. The orange region represents the area of CCDs corresponding to the Suprime-Cam, while the gray region indicates CCDs used for guide. Fully depleted CCDs (FDCCDs) which was developed in collaboration between NAOJ and Hamamatsu Photonics K.K, are employed (Fig. 2.7). The pixel size of the FDCCD is 2048 x 4096 (15  $\mu$ m pixel) which corresponds to 0.17 arcsec in combination with optics and FDCCD has 4 outputs. The important advantage of FDCCD is higher quantum efficiency (QE) in the red band thanks to the thicker depletion layer. FDCCD we developed also has high QE in the blue band due to new backside treatment. FDCCDs are actively cooled down to -100 degree Celsius by cold

Figure 2.7: FDCCD

plane [16] in order to suppress thermal noise and elicit its performance. The specification of FDCCD is shown in table 2.1. Basic specifications such as charge transfer efficiency (CTE), QE, dark current, and readout noise are all met. Refer to Kamata *et al.*[13] for more details.

| Number of Pixels       | 2048 x 4096                          |

|------------------------|--------------------------------------|

| Pixel Size             | $15 \ \mu \mathrm{m}$                |

| Parallel CTE           | 0.999995                             |

| Serial CTE             | 0.999995                             |

| QE                     | 40% (400nm)                          |

|                        | 90% (650  nm)                        |

|                        | 40% (1000 nm)                        |

| Dark Current           | $1.4 \text{ e}^-/\text{hour/pixel}$  |

| Fullwell               | $180,000 e^-$                        |

| Amplifier Responsivity | $5 \ \mu V/e^-$                      |

| Readout Noise          | $4.4\mathrm{e^-}$ at 150 kHz readout |

Table 2.1: FDCCD Specification. All parameters are measured in -100 degree Celsius

## Filter

We are planning to employ the following broadband filters:g(400nm - 550nm), r(550nm - 700nm), i(700nm - 850nm), z(850nm - 1000nm), y(950nm - 1100nm). Overlap between z and y is under consideration.

#### Readout System

Readout system is an electronics which control CCDs, digitize image signal and transfer it to the data acquisition (DAQ) system in control room. Details will be described in the next chapter.

#### 2.3.3 Comparison with other projects

Several wide-field imaging projects for probing dark energy are in progress, which is listed in table 2.2.

The survey speed at which objects can be detected scales as the *etendue* of the telescope, which is defined as the product of the size of its primary mirror (A) times the field of view  $(\Omega)$ .

Pan-STARRS is run by The University of Hawaii. Although the aperture of the telescope is small (1.8 m), using 4 cameras whose FOV is large (3 degrees) provides the high ability of survey. One of the cameras already commenced operation.

The Dark Energy Survey (DES) is run by Fermilab involving the National Optical Astronomy Observatory (NOAO), which succeeds Sloan Digital Sky Survey (SDSS). Since it uses a telescope constructed in 1970's, its imaging ability is worse than Subaru. This is a disadvantage for weak lensing survey.

The Large Synoptic Survey Telescope (LSST) is proposed by SLAC, which has 8.4-m mirror and 7-degree camera. Although its  $A\Omega$  overwhelms other projects, its first light is planned in 2014.

Among these projects, the HSC has the largest  $A\Omega$  and highest imaging quality at the moment of its first light. The HSC will provide data enough to put new restrictions on the nature of dark energy.

| Project    | Telescope     | $A\Omega$    | First Light    |

|------------|---------------|--------------|----------------|

| HSC        | Subaru        | 91           | 2011           |

| DES        | CTIO          | 37           | 2010           |

| Pan-STARRS | New Telescope | $13.4 \ge 4$ | partly started |

| LSST       | New Telescope | 329          | 2014           |

Table 2.2: Ongoing Projects for Probing Dark Energy

# Chapter 3

# Overview of the Readout System for the Hyper Suprime-Cam

The readout system of HSC handles ~ 440 outputs since it employs ~ 110 CCDs and each CCD has 4 outputs. Each CCD has 2048 x 4096 pixels and the readout electronics digitize the image signal into 16 bits. Thus total data size per exposure becomes ~ 2 Gbytes. It is required to read the entire array in 10 seconds in fast readout mode which corresponds to a data rate of 1.6 Gbits/s. Handling this large amount data at high speed is challenging. The noise of the readout electronics should be smaller than that of a CCD  $(\sim 4e^{-})$

| Number of CCD        | ~110                    |

|----------------------|-------------------------|

| Total Signal Outputs | $\sim 440$              |

| Data Resolution      | 16 bits                 |

| Image Size           | $\sim 2 \text{ Gbytes}$ |

| Readout Time         | min. 10sec              |

| Data Rate            | $\sim$ 1.6 Gbps         |

| Readout Noise        | <<4e <sup>-</sup>       |

Table 3.1: Electronics Requirements

# 3.1 Design Concept

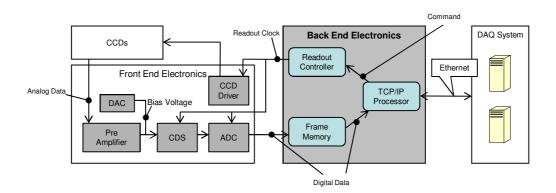

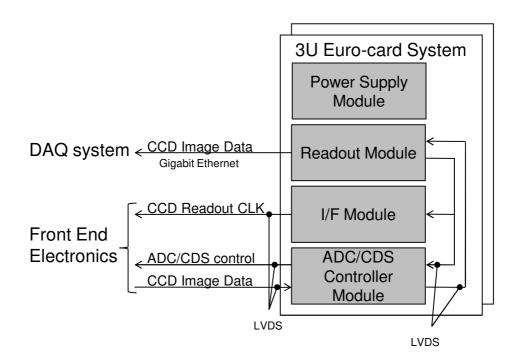

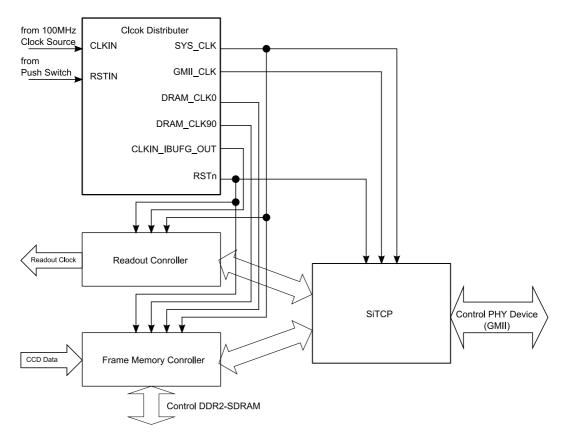

Fig.3.1 shows a block diagram of the readout system for the HSC, which consists of four parts: the CCDs, a DAQ system, a Back End Electronics (BEE), a Front End Electronics (FEE)[15].

The DAQ system controls the overall system and gathers image data from the CCDs. The FEE is an analog part, which consists of mainly five parts: pre-amplifiers, correlated double samplings (CDSs) [19], 16-bit ADCs, digital-to-analog converters (DACs), a CCD

Figure 3.1: A schematic of the readout system for the HSC.

driver. A group consisting of one pre-amplifier, one CDS, one ADC, and one DAC is used for processing a single output from the CCD. The BEE is a digital part which provides the interface between the CCDs, the FEE and the DAQ system. The BEE consists of three blocks: Transmission Control Protocol/Internet Protocol (TCP/IP)[21][22] processor, readout controller, and frame memory. The FEE and the BEE are integrated into the camera unit, while the DAQ system is located in a control room. Since the distance between the FEE and the BEE is large, low voltage differential signalling (LVDS) is used for the signal standard of the communication between the FEE and BEE. Ethernet and TCP/IP are employed for the communication protocol between the BEE and the DAQ system, which has a high degree of reliability and flexibility.

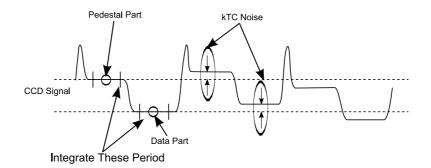

From the DAQ system, commands to control the CCDs and the FEE are sent to the BEE. The readout controller receives these commands through the TCP/IP processor. Following these commands, the readout controller generates readout clocks for the CCDs and the FEE. The readout clock controls the CCDs through the CCD driver which converts the signal level of the readout clock. The analog data is then sent from the CCDs to the FEE. The data is amplified 3-4 fold by the pre-amplifier. The amplified analog data is then sent to the CDS after a bias voltage is added by the DAC, in order to reduce the possibility that the analog image data is cut off from the CDS range when the environment around the CCDs changes. The CDS integrates the data part and the reset part of the analog image signal respectively and outputs the difference of these signals for reducing noise (for details see Fig. 3.2). The integration time of the CDS is controlled by the readout controller of the BEE. The image signal processed by the CDS is then sent to the ADC. The ADC is also controlled by the readout controller of the BEE. After being digitized by the ADC, the image data arrives into the BEE. The whole image data is then stored in the frame memory. The stored image data in the frame memory is transferred to the TCP/IP processor and the image data is transferred to the DAQ system over Ethernet.

Figure 3.2: Correlated Double Sampling of CCD Signal. In a typical CCD signal, the reset part (corresponding to  $0e^-$ ) comes first, and data part (corresponding to the number of electrons which pixel acquired) next. The issue is that there is noise that adds the bias to the whole signal of one pixel, which is called kTC noise. To cancel this noise, the reset part and the data part are integrated respectively and their difference is output. This process is called correlated double sampling.

# **3.2** Front End Electronics

The FEE is under development at the NAOJ. It is essentially same as the MFront2 [15] which is already used as the front end electronics of the existing Suprime-Cam. Functionality of the FEE are as follows.

- Power management

- Voltage, current, and temperature monitor

- shutdown switch in case of fault

- Bias voltage generation and clock driving

- Multiple output DAC, CCD driver

- Output signal processing

- Pre amplifier

- Double slope type CDS

- 16bit ADC

- Digital interface

- CPU

- LVDS interface for the communication with the BEE

In the current design, one FEE board is used for 4 CCDs. Since the CCD has 4 outputs, the single FEE board handles 16 outputs in parallel.  $\sim$ 30 FEE boards are employed for the whole readout system.

Figure 3.3: FEE Boards Alignment. The FEE boards are located under the cold plate in the cryostat

The FEE is located under the cold plate as is shown in Fig.3.3. Although the cold plane is cooled down to -100 degrees Celsius by pulse-tube coolers[16], the FEE is not actively cooled. It is almost the same temperature of the vacuum cryostat wall. This cooled and vacuumed space is one difference from the FEE of the existing Suprime-Cam. Placing a huge volume of electronics inside vacuumed space and keeping the environment cold is challenging.

# 3.3 Back End Electronics

The BEE is under development at the University of Tokyo. The BEE is located outside of the cryostat. Fig3.4 shows the schematic diagram of the planned BEE system. The BEE is consists of two Eurocard systems[17][18]. Each Eurocard system consists of the following modules.

- Power Supply Module This module needs a 5-V power supply and distributes a 5-V and a 3.3-V supply to other BEE modules. The module also pilots the current.

- Readout Module

This module is the main module of the BEE, which has the three functionality of the BEE described in §3.1: the TCP/IP processor, the readout controller and the frame

Figure 3.4: Schematics of a planned BEE system

memory. The single readout module controls half of the CCDs and the FEE. The signal standard of the readout clock and the CCD image data is LVDS. One readout module has one Gigabit Ethernet link for the communication with the DAQ system. Since we employ two Eurocard systems, 2 links of Gigabit Ethernet are used.

• I/F Module

This module drives the LVDS CCD readout clock from the readout module again to fair the signals.

• ADC/CDS Controller Module

This module controls the ADCs/CDSs in the FEE with a Serial Peripheral Interface (SPI), and then transfers digitized image data to the readout module through LVDS signal lines.

We have developed a prototype of the readout module, and discuss details of the module in the next chapter.

# Chapter 4

# R & D of the Readout Module for the Back End Electronics

We have developed the prototype of the readout module which is the main part of the BEE. In this chapter we present the details of the design and architecture of the module, and the result of the performance test.

# 4.1 Requirement

The requirement for the readout module is as follows:

#### • Throughput: 0.8Gbps

It is required that the readout system should send the whole image data of one exposure ( $\sim 2$  Gbytes) to the DAQ system within 10 seconds in the case of the fast readout mode, which corresponds to 1.6 Gbps in throughput. Since we employ two readout modules, the required throughput for the single readout module is 0.8 Gbps.

#### • Large capacity of the frame memory (>~1 Gbyte)

It is required that the readout module has a large frame memory capacity in order to store the entire image data ( $\sim 2$  Gbytes). Since two readout modules are employed in the whole system, the requirement for the single readout module is the frame memory capacity of more than  $>\sim 1$  Gbyte.

#### • Noise $<< 4e^-$ around the bias voltage

The noise from the readout module must be much lower than the noise of the CCD output which is expected to be  $\sim 4 \text{ e}^-$ . However, when the number of electrons is large, the Poisson noise of electron itself is so large that other noise is not important. Thus, the requirement for the noise is that the noise from the readout module should be much lower than that from the CCD in the "few electron region." The few electron region corresponds to the voltage around the bias voltage which the DAC adds before the CDS in the FEE. To summarize, the requirement of the noise of the readout electronics is << 4e<sup>-</sup> around the bias voltage.

#### • Small, light, and low power consumption

Since the readout module will be integrated into the camera unit, this module should be small and light, and its power consumption should be low.

# 4.2 Overview of the readout module

# 4.2.1 Design

The prototype readout module we have developed is called *GESiCA*: Gigabit Ethernet SiTCP CMC board for Astronomy. This module has the following features: small size, light weight, low power consumption, Gigabit Ethernet, a large memory capacity, and low clock jitter for the readout clocks.

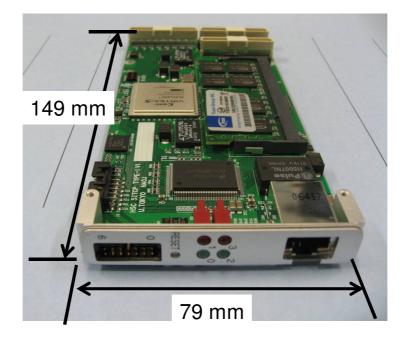

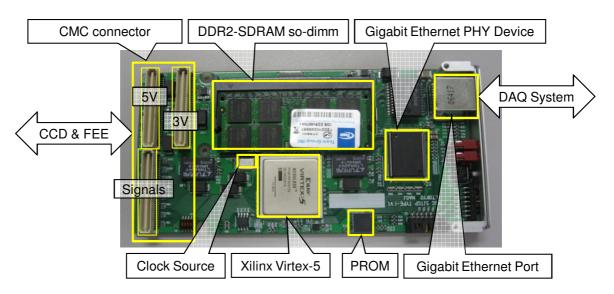

Fig.4.1 and Fig.4.2 are pictures of GESiCA. Its size is 149 mm  $\times$  79 mm  $\times$  12 mm and weight is  $\sim$  100 g, which is compatible with the Common Mezzanine Card (CMC) specified as IEEE P1386 [25]. Generally, CMC are designed to be plugged into a slot on a host's mother board. GESiCA is integrated into the BEE through a host board in 3U Eurocard size. Note that GESiCA is independent of a system of host modules, so various systems can be used in different phases of development. For instance, to evaluate performance, we combined GESiCA to a part of the current Suprime-Cam system, whose detail will be described in Chapter 5.

Main parts of GESiCA are the CMC connectors, a Gigabit Ethernet Physical Layer Device (PHY; DP83865DVH, National Semiconductor Corp.), a Double-Data-Rate2 Synchronous Dynamic Random Access Memory (DDR2 SDRAM) Small Outline Dual In-line Memory Module (SO-DIMM), a Field Programmable Gate Array (FPGA; XC5LVX110-FFG676-2I, Xilinx Inc.), and a low-jitter clock source.

### • CMC connectors

GESiCA has three CMC connectors. Two connectors are used for supplying power (5V and 3.3V for each connector).

The other one connecter is used for communication signals. All pins of this connector are connected directly to the FPGA. The most pins of this connector are mainly used for the communication between GESiCA, the CCDs and the FEE. The readout clock is sent to the CCDs and the FEEs through this connector, and the image data comes back to GESiCA also through this connector. The other pins of the connector will be used for the other general purpose such as sending commands to shutter. Pin assignment of this connector is shown in table4.1. Communication protocol adheres to the original specification of the NAOJ. Signal standard is complementary metal oxide semiconductor (CMOS) 3.3V, which are converted to LVDS on the host board in the HSC system.

#### • Gigabit Ethernet PHY device

As an interface between GESiCA and the DAQ system, we employ the PHY and one Gigabit Ethernet 1000BASE-T port with Unshielded Twisted Pair cabling (UTP). Since two GESiCAs will be employed, two links of Gigabit Ethernet will be used for

Figure 4.1: Photograph of prototype readout module (GESiCA) (front view)

Figure 4.2: Photograph of prototype readout module (GESiCA) (top view)

the HSC readout system, which meets the requirement of throughput for the whole HSC system ( $\sim 1.6$  Gbps).

## • DDR2 SDRAM SO-DIMM

The DDR2 SDRAM SO-DIMM plays the role of the frame memory with the capacity of up to 2 Gbytes. The capacity is enough to store temporarily image data because one GESiCA processes half of the CCDs - the total size is about 2 Gbytes per exposure.

#### • FPGA

The FPGA controls the PHY and the DDR2 SDRAM SO-DIMM, and generates the readout clock for the CCDs and the FEE. The FPGA can be configured by Programmable Read Only Memory (PROM) which can be overwritten by computer through the Joint Test Action Group (JTAG).

## • Low-jitter clock source

The FPGA generates a 32-bit readout clock to control the CCD and the FEE. We described how the readout clock controls the FEE in §3.1. The jitter of the readout clock which controls the CDS creates noise. In order to make the noise low, it is necessary to use a low-jitter clock source. Thus, we mounted an Epson Toyocom XG-1000CA whose jitter is 3-ps (typical) root mean square on GESiCA. The result of the test for the noise will be described in §4.4.3.

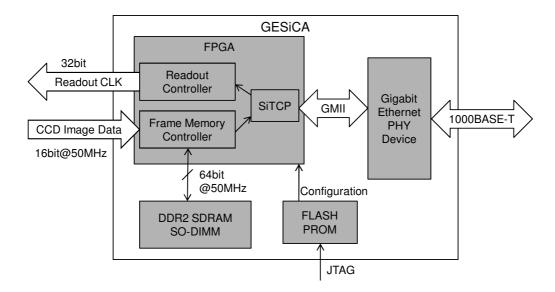

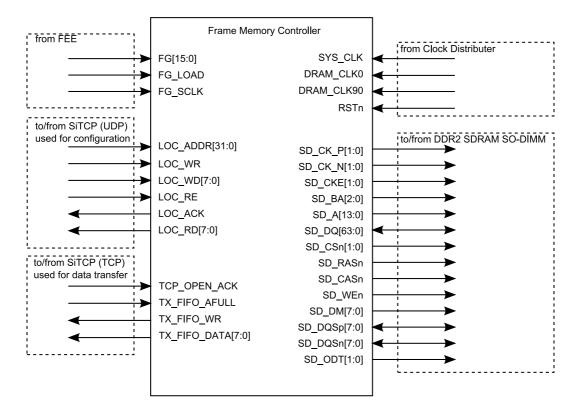

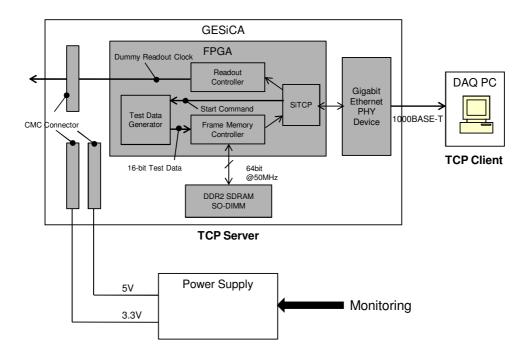

# 4.2.2 Operation

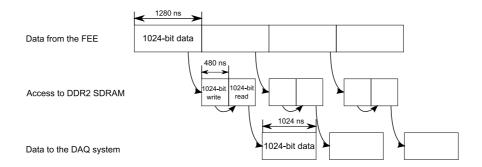

Fig.4.3 is a block diagram of GESiCA. The FPGA contains three blocks: a hardware-based TCP/IP processor (SiTCP) [26], readout controller, and frame memory controller. The PHY and SiTCP are connected with the standard interface, Gigabit Media Independent Interface (GMII)specified by IEEE 802.3[23]. Receiving commands from the DAQ system through SiTCP, the readout controller generates 32-bit CMOS 3.3V readout clocks which controls CCD and FEE through the CMC connectors. The frame memory controller then grabs 16-bit digitized image data from the FEE through the CMC connectors and writes the image data to the frame memory (DDR2 SDRAM). The image data is then read from the frame memory and sent to DAQ system through SiTCP. It should be noted that the DDR2 SDRAM is controlled in the clock frequency of 50 MHz in GESiCA, while the standard requires 125 MHz or higher[29].

### 4.2.3 Communication with the DAQ system

GESiCA can be seen as a TCP server from the DAQ system. The user can control GESiCA by using a socket software.

The image data is sent from to the DAQ system over Transmission Control Protocol (TCP), while other communication with the DAQ system, including commands to the the readout controller, are established over User Datagram Protocol (UDP) [20]. TCP has the high reliability of data transfer. UDP sends packets as quick as a user commands. Thus

| Pin Number | Signal  | Pin Number | Signal |

|------------|---------|------------|--------|

| 1          | P_IN0   | 33         | CP0    |

| 2          | RESET   | 34         | CP1    |

| 3          | P_IN1   | 35         | CP2    |

| 4          | SYNC0   | 36         | CP3    |

| 5          | P_IN2   | 37         | CP4    |

| 6          | ACTIVE  | 38         | CP5    |

| 7          | P_IN3   | 39         | CP6    |

| 8          | SYNC1   | 40         | CP7    |

| 9          | P_OUT0  | 41         | CP8    |

| 10         | UART0   | 42         | CP9    |

| 11         | P_OUT1  | 43         | CP10   |

| 12         | FG_SCLK | 44         | CP11   |

| 13         | P_OUT2  | 45         | CP12   |

| 14         | UART1   | 46         | CP13   |

| 15         | P_OUT3  | 47         | CP14   |

| 16         | FG_LOAD | 48         | CP15   |

| 17         | FG0     | 49         | CP16   |

| 18         | FG1     | 50         | CP17   |

| 19         | FG2     | 51         | CP18   |

| 20         | FG3     | 52         | CP19   |

| 21         | FG4     | 53         | CP20   |

| 22         | FG5     | 54         | CP21   |

| 23         | FG6     | 55         | CP22   |

| 24         | FG7     | 56         | CP23   |

| 25         | FG8     | 57         | CP24   |

| 26         | FG9     | 58         | CP25   |

| 27         | FG10    | 59         | CP26   |

| 28         | FG11    | 60         | CP27   |

| 29         | FG12    | 61         | CP28   |

| 30         | FG13    | 62         | CP29   |

| 31         | FG14    | 63         | CP30   |

| 32         | FG15    | 54         | CP31   |

Table 4.1: Pin assignment of the CMC connector of GESiCA. PIN0-3/POUT0-3 are general purpose inputs/outputs. RESET is used for master reset. ACTIVE is used for return from sleep. SYNC0-1 are used for synchronization of readout modules. UART0-1 are used for serial communication. The signals mentioned above will be used in the future. FG\_SCLK and FG\_LOAD are the control signal from the FEE. FG0-15 is the 16-bit digital image data from the FEE. CP0-31 is the 32-bit readout clock for the CCDs and the FEE.

Figure 4.3: A block diagram of GESiCA

safety of image data transfer is insured and commands can be sent on the timing a user indicates.

#### Communication over TCP

While TCP connection is established, the DAQ system can receive the image data from GESiCA. The header is added to the beginning of each exposure. The specification of the header is shown in Fig.4.4. Version indicates the current GESiCA version. Data Length indicates the number of the whole image data in units of byte. Frame ID is incremented everytime new exposure is taken. R0-R6 are the registers a user can configure freely, which is prepared for future use. All parameters are in network byte order (big endian).

Figure 4.4: Image Data Header Specification. The size of the header is 32 bytes.

# Communication over UDP

Using communication over UDP, a user can edit the configuration of GESiCA and send commands to GESiCA.

• configuration

exposure size

It is necessary to set the number of pixels per exposure in order to tell GESiCA where it should add the header of the image data.

- readout clock pattern

GESiCA stores patterns of the readout clock inside. A user can configure the patterns of the readout clock.

- command

- invoke

Start a pattern of the readout clock.

- reset

Stop the readout clock. All outputs goes to low level.

- busy?

This command is used to ask the state of GESiCA. If the readout controller generates the readout clock, GESiCA returns busy. If not, it returns idle.

Details of these configuration and commands are described in Appendix.A.2.

# 4.3 FPGA implementation

In the following sections, we will explain details about the FPGA implementation.

#### 4.3.1 Clock Management

Fig.4.5 shows clock distribution in the FPGA. The clock distributer which contains four Digital Clock Managers (DCMs) built in the FPGA[28] provides all the clocks used in the FPGA. Referencing the input clock (100MHz; Epson Toyocom XG-1000CA), a DCM generates a clock whose period and phase are specified by a user. The clock distributer provides the following clocks.

• SYS\_CLK

The frequency of SYS\_CLK is 130MHz. This clock is used as a system clock of the FPGA which is distributed to the SiTCP, readout controller, and frame memory controller.

• GMII\_CLK

The frequency of GMII\_CLK is 125MHz. This clock is provided to SiTCP and used as the GMII clock for communication with the PHY device.

## • DRAM\_CLK0, DRAM\_CLK90

The frequency of these clocks is 50MHz. The phase of DRAM\_CLK90 is shifted by 90 degrees compared to DRAM\_CLK0. These clocks are provided to the frame memory controller and used to control the DDR2 SDRAM SO-DIMM.

Figure 4.5: Clock Distribution in FPGA

### • CLKIN\_IBUFG\_OUT

CLKIN\_IBUFG\_OUT outputs the clock from the clock source without any modification. This clock is provided to the readout controller and used for the readout clock to make the most of the low-jitter clock source and minimize the noise of the electronics (see §4.2.1).

# • RSTn

RSTn is an active-low reset signal distributed to the SiTCP, readout controller and frame memory controller. While RSTIN, which is connected to an active-low push switch on GESiCA, is negated, all of the DCMs are reset and the RSTn is negated, that is, the reset signal propagates over the FPGA. After the RSTIN is asserted and initializations of all the DCMs are completed, the RSTn is asserted.

# 4.3.2 SiTCP

SiTCP is a hardware-based TCP/IP processor[26], which provides the Gigabit Ethernet connection between the DAQ system and GESiCA. SiTCP offers a solution for the following requirements:

- Throughput: 0.8Gbps

- Small, light, and low power consumption

Generally, TCP/IP is processed by software running on a standard operating system. A powerful hardware and CPU are required to process these protocols at gigabit rates, and thus power consumption becomes of order several tens of watts and the size and weight are both large. SiTCP is able to overcome these difficulties. The logic size of SiTCP is small enough to allow us to implement it on a single FPGA. This feature enables us to design a small, light and low-power consumption module that has high speed data transfer capability at the same time.

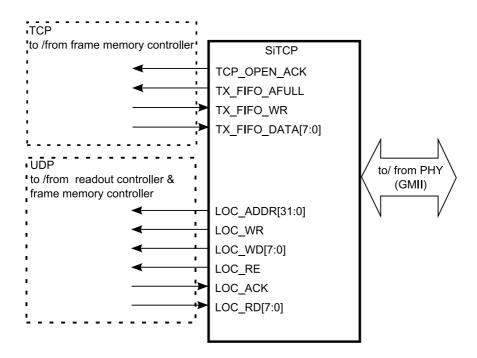

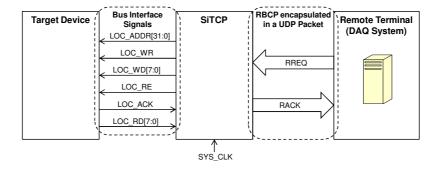

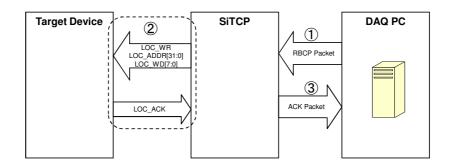

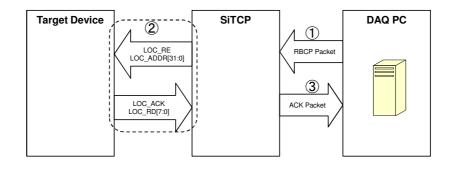

Fig.4.6 represents I/O of SiTCP. SiTCP controls the PHY Device through GMII and has user interface signals for TCP and UDP whose details are shown in table 4.2. To communicate with GESiCA over UDP, a user should use an original protocol called Remote Bus Control Protocol (RBCP), which is encapsuled in UDP packets. Details of RBCP are described in Appendix.A.1.

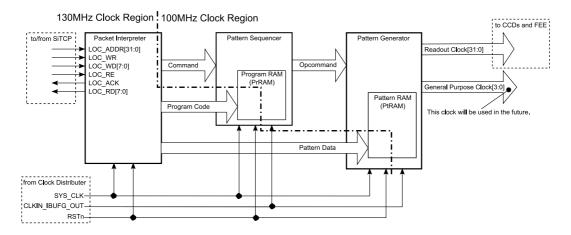

# 4.3.3 Readout Controller

#### Functionality

The readout controller generates a 32-bit readout clock to control the CCDs and the FEE, following commands from the DAQ system. This module can also generate additional a 4-bit control clock for general purpose (P\_OUT[3:0] in Appendix.A) which will be used in the future. Hereafter, the 32-bit readout clock + 4-bit general purpose clock is simply called the readout clock. These signals are sent to the outside of GESiCA through the a CMC connector.

Figure 4.6: I/O of SiTCP

| Category | Signal        | Description                                     |  |

|----------|---------------|-------------------------------------------------|--|

| TCP      | TCP_OPEN_ACK  | Acknowledge: When asserted, TCP connec-         |  |

|          |               | tion is established.                            |  |

|          | TX_FIFO_AFULL | Almost full flag: When asserted, the buffer for |  |

|          |               | TX_FIFO_DATA in SiTCP can perform only          |  |

|          |               | 8 more write.                                   |  |

|          | TX_FIFO_WR    | Write enable: If the buffer in the SiTCP is     |  |

|          |               | not full, asserting this signal causes data (on |  |

|          |               | TX_FIFO_DATA) to be written to the buffer       |  |

|          | TX_FIFO_DATA  | 8-bit width write data                          |  |

| UDP      | LOC_ADDR      | 32-bit width address                            |  |

|          | LOC_WR        | Write enable                                    |  |

|          | LOC_WD        | 8-bit width write data                          |  |

|          | LOC_RE        | Read enable                                     |  |

|          | LOC_ACK       | Access acknowledge from target devices. In      |  |

|          |               | read access, valid read data                    |  |

|          | LOC_RD        | 8-bit width read data                           |  |

Table 4.2: User Interface Signals of SiTCP

The readout controller provides the following solution for the requirement presented in §4.1.

• low-jitter readout clock

As mentioned in §3.1 and §4.2.1, the low-jitter readout clock for controlling integration period of the CDS is crucial to realize low noise. The readout controller uses the clock directly from the low-jitter clock source to generate low-jitter readout clocks (cf. §4.2.1). The estimation of the noise resulting from the jitter will be described in §4.4.3.

In addition, the readout controller has the following features

• fine tuning capability of the readout clock